# **CENESAS**

RE01 Group (256-KB Flash Memory)

### Renesas Microcontrollers

# Datasheet

R01DS0369EJ0100 Rev.1.00 Apr 3, 2020

64 MHz, 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M0+, 256-KB flash memory, 128-KB SRAM, energy harvesting control circuit, MIP LCD controller, 2D graphic engine, 14-bit ultra-low power consumption A/D converter, VREF circuit, RTC, sub-clock correction circuit (theoretical regulation), security function (optional), SPI, quad SPI

# Features

- Arm Cortex-M0+ core incorporated

- Maximum operating frequency: 64 MHz

- Arm<sup>®</sup> Memory Protection Unit (Arm MPU) with 8 regions

- CoreSight<sup>™</sup> Debug Port: SW-DP

#### Power-aving functions

- · Back-bias control function based on silicon-on-thin-buried-oxide (SOTB<sup>™</sup>) process technology

- Operation at ultra-low power-supply voltages (from 1.62 V to 3.6 ٧Ĵ

- · Three power control modes based on the operating frequency

- Four low power consumption modesThree power supply modes

#### On-chip Code flash memory

- 256-Kbyte code flash memory

- No cycles of waiting for access in operation at or below 32 MHz; one cycle of waiting at frequencies above 32 MHz

- · Function for area protection prevents erroneous overwriting or tampering

#### On-chip SRAM

· 128-Kbyte SRAM with no access wait cycles

#### Data transfer

- Four DMA controllers

- Single data transfer controller (DTC)

#### Reset and supply management

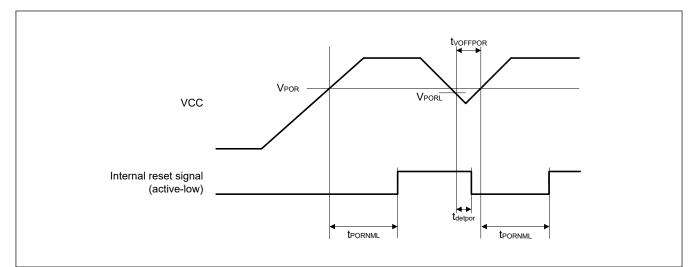

- Power-on reset (POR)

- · Low voltage detection (LVD) can be set.

#### Multiple clock sources

- External crystal oscillator (main clock): 8 to 32 MHz

- External crystal oscillator (main clock): 30: 352 MHz

External crystal oscillator (sub-clock): 32: 768 kHz

High-speed on-chip oscillator (HOCO): 24, 32, 48, or 64 MHz

Middle-speed on-chip oscillator (MOCO): 2 MHz

Low-speed on-chip oscillator (LOCO): 32 kHz

- Independent watchdog timer on-chip oscillator: 16 kHz

#### Energy harvesting control

- A power generation element is directly connectable.

- High-speed startup is possible without having to wait for the charging of a secondary battery.Function to prevent a secondary battery from overcharging

#### Independent watchdog timer

• 14-bit counter, 16-kHz (1/2 LOCO clock frequency) operation

#### Sub-clock correction circuit (CCC)

- The CCC corrects the accuracy of oscillation every 16 seconds

- (theoretical regulation). Èvents can be generated per second in deep software standby mode.

#### Communication functions

- Two serial peripheral interfaces Single 128-bit buffer for which up to eight commands can be specified

- Single 32-bit buffer for which one command can be specified • Single quad serial peripheral interface connectable to an external flash memory

- Two I<sup>2</sup>C bus interfaces

- Five serial communications interfaces (SCIg) Asynchronous, clock-synchronous, simple I<sup>2</sup>C, simple SPI, and smart card interfaces, and IrDA interface version 1.0 (the latter is only applicable to SCI0)

- Two serial communication interfaces (SCIi) each having a 16-byte FIFO

#### Various analog circuits

- Single 14-bit successive approximation A/D converter High precision: 8 channels, standard precision: 4 channels

- Single temperature sensor for measuring the internal temperature of the chip

- VREF circuit for the 14-bit A/D converter reference voltage

#### Various timer circuits

- Six general PWM timers (GPT) Two 32-bit counters

- Four 16-bit counters

- Four asynchronous general-purpose timers (AGT) that can be used in standby mode Two 32-bit counters

- Two 16-bit counters

- Two 8-bit timers (TMR)

- Single realtime clock (RTC)

- Single watchdog timer (WDT) Single low-speed timer (LST) that operates at 1 kHz ٠ A circuit for converting hexadecimal numbers to decimal numbers for use as a stopwatch

- Human machine interfaces

- Single memory-in-pixel (MIP) LCD controller (MLCD) Parallel interface is supported.

- Single 2D graphics data conversion circuit (GDT)

#### Security functions (optional)

- Single Trusted Secure IP Lite (TSIP)

- AES (128- or 256-bit key length, supporting ECB, CBC, CMAC, GCM, and others)

- Key wrapping protects against the leakage of the encryption keys of users.

- An access management circuit disables illicit access to the encryption engine.

- Using the other security functions together with area protection enables secure booting and secure over-the-air (OTA) software updates.

#### Operating voltage and temperature range

- VCC = IOVCC = IOVCCn = AVCC0 = 1.62 V to 3.6 V IOVCCn and AVCC0 can each be independently set to a voltage within the range between 1.62 V and 3.6 V. • Ta: -40 to +85°C

# 1. Overview

# 1.1 Function Outline

Table 1.1 to Table 1.11 show the outline of maximum specifications. The number of peripheral channels differs depending on the number of pins of the package. For details, see Table 1.13.

# Table 1.1 Arm core

| Feature                                        | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arm <sup>®</sup> Cortex <sup>®</sup> -M0+ core | <ul> <li>Maximum operating frequency: up to 64 MHz</li> <li>Arm Cortex-M0+ core: <ul> <li>Revision: r0p1-00rel0</li> <li>Armv6-M architecture profile</li> <li>Single-cycle integer multiplier</li> </ul> </li> <li>Arm Memory Protection Unit (MPU): <ul> <li>Armv6 Protected Memory System Architecture</li> <li>Eight protect regions</li> </ul> </li> <li>SysTick timer: <ul> <li>Driven by SYSTICCLK (LOCO or ICLK)</li> </ul> </li> </ul> |

### Table 1.2 Memory

| Feature           | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Code flash memory | <ul> <li>Maximum 256 KB of code flash memory.</li> <li>No cycles of waiting for access in operation at or below 32 MHz; one cycle of waiting at frequencies above 32 MHz</li> <li>Prefetch function</li> <li>On-board programming (three types): <ul> <li>Programming in serial programming mode (SCI boot mode)</li> <li>Programming in on-chip debug mode</li> <li>Programming by a routine for code flash memory rewriting within a user program</li> </ul> </li> </ul> |

| SRAM              | <ul> <li>Maximum 128 KB of SRAM<br/>SRAM0: 0x2000_0000 to 0x2000_7FFF<br/>SRAM1: 0x2000_8000 to 0x2001_FFFF<br/>Both areas are available during low leakage current mode.</li> <li>64 MHz, No cycles of waiting for access</li> </ul>                                                                                                                                                                                                                                      |

### Table 1.3System (1 of 2)

| Feature                     | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

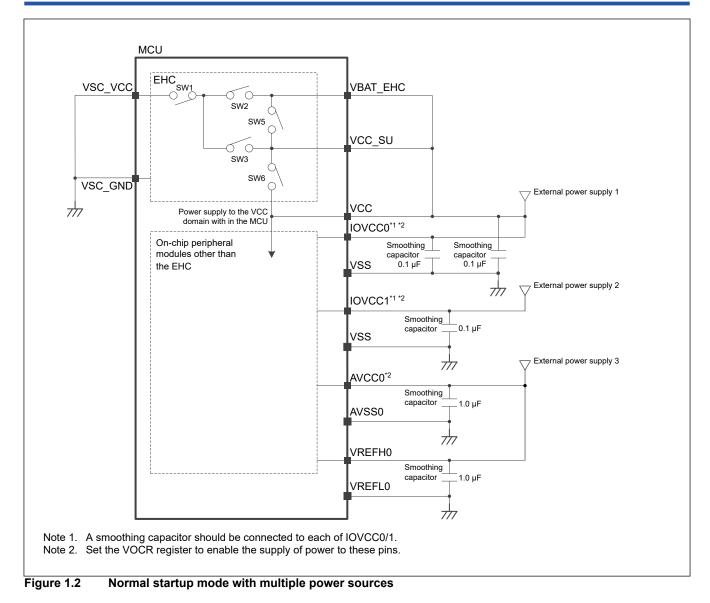

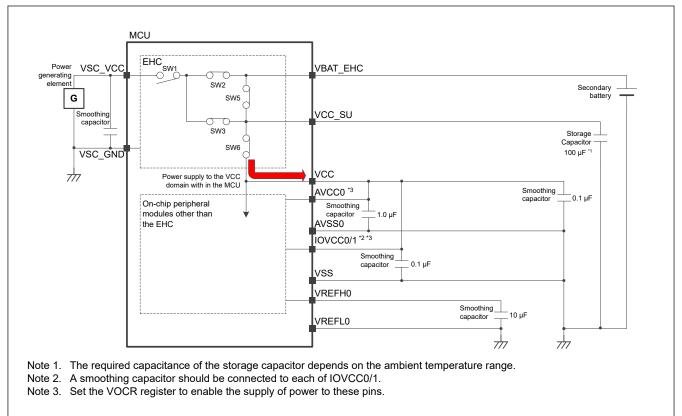

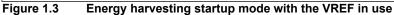

| Startup modes               | Three startup modes:<br>• Normal startup mode<br>• Energy harvesting startup mode<br>• SCI boot mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Resets                      | The MCU provides 13 resets. The resets are classified into two types: System resets that initialize the MCU and power shutdown reset that does not initialize the MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

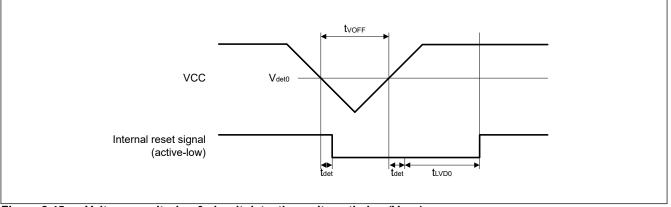

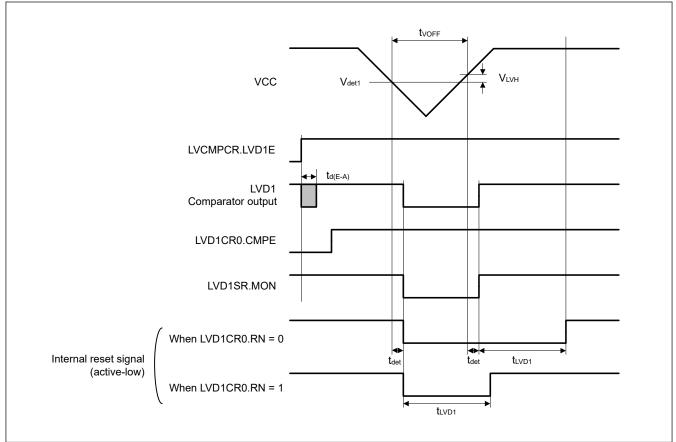

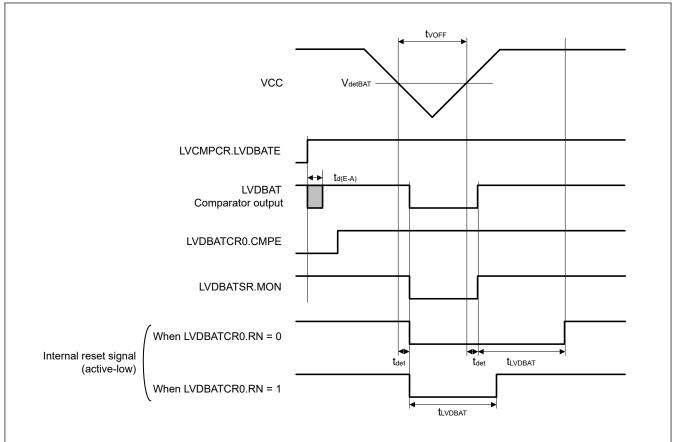

| Low Voltage Detection (LVD) | The Low Voltage Detection (LVD) module monitors the voltage level input to the VCC pin and VBAT_EHC pin. The detection level can be selected by register settings. The LVD module consists of three separate voltage level detectors (LVD0, LVD1, LVDBAT). LVD0 and LVD1 measure the voltage level input to the VCC pin, and LVDBAT measures the voltage level input to the VCC pin, and LVDBAT measures the voltage level input to the VBAT_EHC pin. LVD registers allow your application to configure detection of VCC and VBAT_EHC changes at various voltage thresholds.                                     |

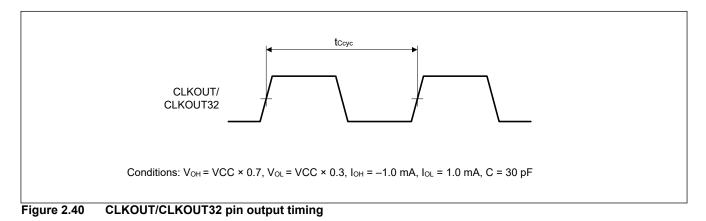

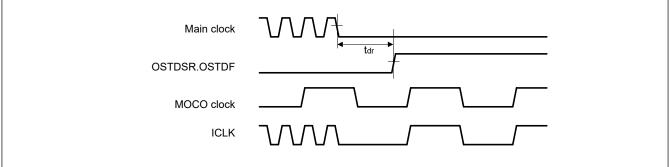

| Clocks                      | <ul> <li>The MCU has the following clock generation circuits.         <ul> <li>Main clock oscillator (MOSC)</li> <li>Sub-clock oscillator (SOSC)</li> <li>High-speed on-chip oscillator (HOCO)</li> <li>Middle-speed on-chip oscillator (MOCO)</li> <li>Low-speed on-chip oscillator (LOCO)</li> <li>Low-speed on-chip oscillator (LOCO)</li> <li>IWDT-dedicated on-chip oscillator (IWDTLOCO)</li> </ul> </li> <li>Clock output support         <ul> <li>CLKOUT pin (capable of outputting all types of clock signals)</li> <li>CLKOUT32K pin (capable of outputting SOSC clock signals)</li> </ul> </li> </ul> |

# Table 1.3 System (2 of 2)

| Feature                                                 | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Frequency Accuracy<br>Measurement Circuit (CAC)   | The Clock Frequency Accuracy Measurement Circuit (CAC) counts pulses of the clock to be measured (measurement target clock) within the time generated by the clock selected as the measurement reference (measurement reference clock), and determines the accuracy depending on whether the number of pulses is within the allowable range. When measurement is complete or the number of pulses within the time generated by the measurement reference clock is not within the allowable range, an interrupt request is generated.                                                                                                                                                                                                                                        |

| Interrupt Controller Unit (ICU)                         | The Interrupt Controller Unit (ICU) controls which event signals are linked to the Nested Vector Interrupt Controller (NVIC), the DMA Controller (DMAC), and the Data Transfer Controller (DTC) modules. The ICU also controls non-maskable interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Power-saving functions                                  | The MCU has several functions for power saving, such as setting clock dividers, stopping<br>modules, selecting power control mode in operating mode, transitioning to low power<br>consumption mode, and power supply mode per domain.<br>• Three power control modes based on the operating frequency<br>– Boost mode (up to 64 MHz)<br>– Normal mode<br>• High-speed mode (up to 32 MHz)<br>• Low-speed mode (up to 2 MHz)<br>• Low-speed mode (up to 2 MHz)<br>– Low leakage current mode (32.768 kHz)<br>• Five low-power consumption modes<br>– Operating mode<br>– Sleep mode<br>– Sleep mode<br>– Software standby mode<br>– Deep software standby mode<br>• Three power supply modes<br>– All-power supply mode (ALLPWON)<br>– Kinnimum power supply mode (MINPWON) |

| Back-bias voltage control <sup>*1</sup> (VBBC) function | Program control of the back bias voltage enables low leakage current operation in the low leakage current mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

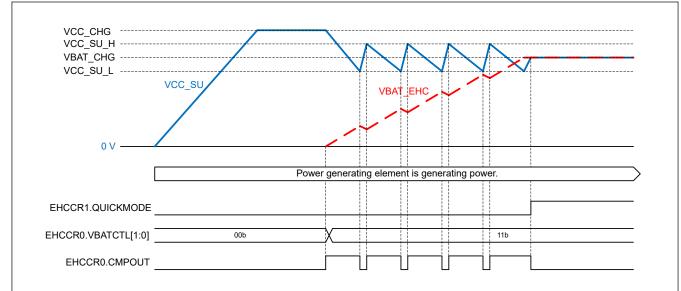

| Energy harvesting control circuit (EHC)                 | Starting up of the MCU in the power-saving mode is possible by controlling the power generating element, storage capacitor, and secondary battery.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Register write protection (RWP)                         | The register write protection function protects important registers from being overwritten due to software errors. The registers to be protected are set with the Protect Register (PRCR).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Memory Protection Unit (MPU)                            | The MCU has four Memory Protection Units (MPUs) and a CPU stack pointer monitor function are provided.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Key Interrupt Function (KINT)                           | The key interrupt function (KINT) is generated a key interrupt by detecting a valid edge on the key interrupt input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# Note 1. Voltage for charging the VBP and VBN pins

#### Table 1.4 Event link

| Feature                     | Functional description                                                                                                                                                                                                                                                                                                    |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Event Link Controller (ELC) | The Event Link Controller (ELC) uses the interrupt requests generated by various peripheral modules as event signals to interconnect (link) modules, allowing direct link between modules without CPU intervention. Event signals can be output regardless of the setting of the associated interrupt request enable bit. |

### Table 1.5Direct memory access

| Feature                        | Functional description                                                                                                                                                                                                                                                         |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA Controller (DMAC)          | This MCU incorporates an 4-channel direct memory access controller (DMAC). The DMAC is a module to transfer data without the CPU. When a DMA transfer request is generated, the DMAC transfers data stored at the transfer source address to the transfer destination address. |

| Data Transfer Controller (DTC) | A Data Transfer Controller (DTC) module is provided for transferring data when activated by an interrupt request.                                                                                                                                                              |

#### Table 1.6 Timers

| Feature                                                     | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General PWM Timer (GPT)                                     | The General PWM Timer (GPT) is a 32-bit timer with GPT32 × 2 channels and a 16-bit timer with GPT16 × 4 channels. PWM waveforms can be generated by controlling the up-counter, down-counter, or the up- and down-counter.                                                                                                                                                                                                                                                                                                                                                                         |

| Port Output Enable for GPT (POE)                            | The Port Output Enable (POE) function can place the General PWM Timer (GPT) output pins in the output disable state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

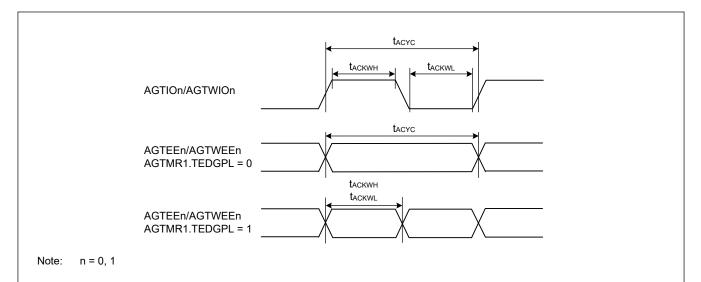

| Low power Asynchronous General<br>Purpose Timer (AGT, AGTW) | The low power Asynchronous General Purpose Timer (AGT, AGTW) is a 16-bit, 32-bit timer that can be used for pulse output, external pulse width or period measurement, and counting external events. This timer consists of a reload register and a down counter. The reload register and the down counter are allocated to the same address, and can be accessed with the AGT register.                                                                                                                                                                                                            |

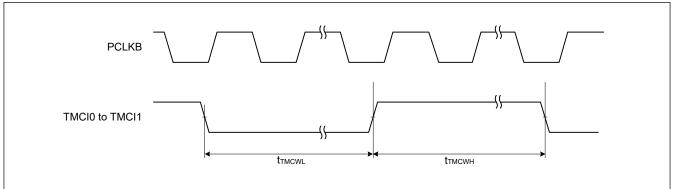

| 8-bit timers (TMR)                                          | 8-bit timer (TMR) can count external events and provide multiple functions such as clearing counters, and outputting interrupt requests and pulses of required duty cycles, using the compare match signals with two registers.                                                                                                                                                                                                                                                                                                                                                                    |

| Wake Up Timer (WUPT)                                        | The wake up timer based on 32-bit counter provides multiple functions such as resetting count, and outputting interrupt requests and pulses to external pins when an overflow occurs.                                                                                                                                                                                                                                                                                                                                                                                                              |

| Realtime Clock (RTC)                                        | The realtime clock (RTC) has three counting modes, calendar count mode, binary count mode, and 32-kHz count mode, that are used by switching register settings. For calendar count mode, the RTC has a 100-year calendar from 2000 to 2099 and automatically adjusts dates for leap years. For binary count mode, the RTC counts seconds and retains the information as a serial value. Binary count mode can be used for calendars other than the Gregorian (Western) calendar.                                                                                                                   |

| Clock Correction Circuit (CCC)                              | <ul> <li>The CCC corrects the oscillation accuracy every 16 seconds for the 32.768-kHz subclock.</li> <li>Clock output after correction: 2.048 kHz/512 Hz</li> <li>Signal output (CCCOUT): Selectable from 512 Hz/1 Hz, or RTC output (1 Hz/64 Hz)</li> <li>Support of function for event linking by the ELC</li> </ul>                                                                                                                                                                                                                                                                            |

| Watchdog Timer (WDT)                                        | The Watchdog Timer (WDT) is a 14-bit down counter that can be used to reset the MCU when the counter underflows because the system has run out of control and is unable to refresh the WDT. In addition, the WDT can be used to generate a non-maskable interrupt or an underflow interrupt.                                                                                                                                                                                                                                                                                                       |

| Independent Watchdog Timer (IWDT)                           | The Independent Watchdog Timer (IWDT) consists of a 14-bit down counter that must be serviced periodically to prevent counter underflow. The IWDT provides functionality to reset the MCU or to generate a non-maskable interrupt or an underflow interrupt. Because the timer operates with an independent, dedicated clock source, it is particularly useful in returning the MCU to a known state as a fail-safe mechanism when the system runs out of control. The IWDT can be triggered automatically by a reset, underflow, refresh error, or a refresh of the count value in the registers. |

| Low-Speed Clock Timer (LST)                                 | <ul> <li>The low-speed clock timer (LST) contains a 1-kHz timer-counter and a circuit for converting hexadecimal numbers to decimal numbers. This is a 13-bit timer that can be used to indicate a count that needs to be displayed in decimal.</li> <li>Capable of counting from 0.000 to 1.999 seconds (in units of 0.001 seconds)</li> <li>A value in decimal notation can be directly stored in a register</li> </ul>                                                                                                                                                                          |

# Table 1.7Communication interfaces (1 of 2)

| Feature                               | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

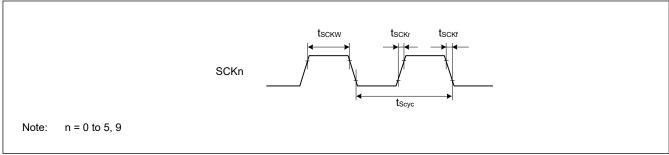

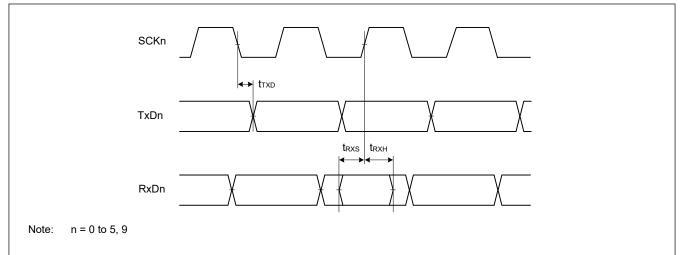

| Serial Communications Interface (SCI) | <ul> <li>The Serial Communications Interface (SCI) × 7 channels have asynchronous and synchronous serial interfaces:</li> <li>Asynchronous interfaces (UART and Asynchronous Communications Interface Adapter (ACIA))</li> <li>8-bit clock synchronous interface</li> <li>Simple IIC (master-only)</li> <li>Simple SPI</li> <li>Smart card interface</li> <li>The smart card interface complies with the ISO/IEC 7816-3 standard for electronic signals and transmission protocol. SCIn (n = 0, 1) has FIFO buffers to enable continuous and full-duplex communication, and the data transfer speed can be configured independently using an on-chip baud rate generator.</li> </ul> |

| IrDA Interface (IrDA)                 | The IrDA (Infrared Data Association) interface sends and receives IrDA data communication waveforms in association with SCI1 based on the IrDA standard 1.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 1.7 | Communication interfaces (2 of 2) |  |

|-----------|-----------------------------------|--|

|-----------|-----------------------------------|--|

| Feature                                | Functional description                                                                                                                                                                                                                                                                                   |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

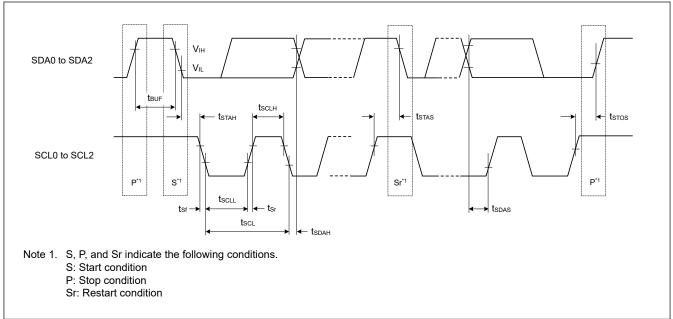

| I <sup>2</sup> C bus interface (IIC)   | The I <sup>2</sup> C bus interface (IIC) has 2 channels. The IIC module conforms with and provides a subset of the NXP I <sup>2</sup> C (Inter-Integrated Circuit) bus interface functions.                                                                                                              |

| Serial Peripheral Interface (SPI)      | The SPI provides high-speed full-duplex and transmit-only synchronous serial communications with multiple processors and peripheral devices.                                                                                                                                                             |

| Quad Serial PeripheralInterface (QSPI) | <ul> <li>The QSPI is connectable to a serial ROM that has an SPI-compatible interface.</li> <li>1 channel</li> <li>Support for extended SPI, dual SPI, and quad SPI protocols</li> <li>Configurable to SPI mode 0 and SPI mode 3</li> <li>Address width selectable from 8, 16, 24, or 32 bits</li> </ul> |

| External bus                           | QSPI area: Connectable to the QSPI (external device interface)                                                                                                                                                                                                                                           |

# Table 1.8 Analog

| Feature                                     | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

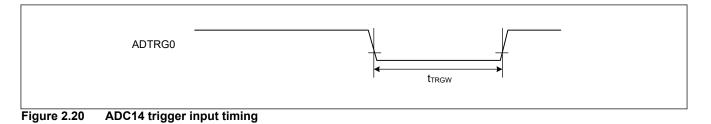

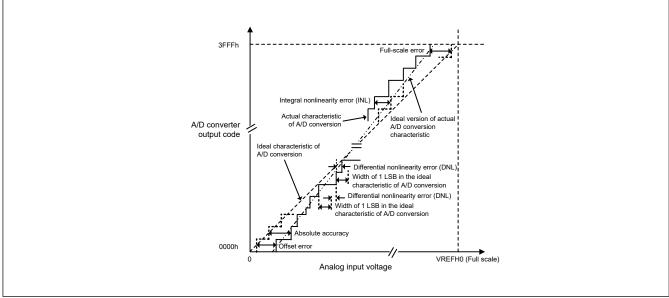

| 14-bit A/D Converter (ADC14)                | <ul> <li>A 14-bit successive approximation A/D converter incorporated</li> <li>Up to 12 analog input channels are selectable. The analog input channels and the temperature sensor output are selectable for conversion. The A/D conversion accuracy is selectable between 12-bit and 14-bit conversion making it possible to optimize the tradeoff between speed and resolution in generating a digital value.</li> <li>14 bits × 12 channels (maximum value) (high accuracy: 8 channels, standard accuracy: 4 channels)</li> <li>Resolution: 14 bits (14-bit or 12-bit conversion selectable)</li> <li>Operating mode: Scan mode, continuous-scan mode, or group-scan mode)</li> <li>Group A priority control (only for group-scan mode)</li> <li>Variable sampling state count</li> <li>A/D-converted value addition mode or average mode selectable</li> <li>Disconnection detection assist function</li> <li>Double-trigger mode (duplication of A/D conversion data)</li> <li>Support of function for event linking by the ELC</li> <li>Automatic clear function of A/D data registers</li> <li>Compare function for window A and window B</li> <li>Digital compare function</li> <li>Comparison of values in the comparison register and the data register, and comparison between values in the data registers</li> </ul> |

| Temperature Sensor (TSN)                    | The on-chip Temperature Sensor (TSN) determines and monitors the die temperature for reliable operation of the device. The sensor outputs a voltage directly proportional to the die temperature, and the relationship between the die temperature and the output voltage is fairly linear. The output voltage is provided to the ADC14 for conversion and can be further used by the end application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Reference voltage generation circuit (VREF) | The circuit generates two types (1.25 V/2.5 V) of reference voltage.<br>The generated voltage can be used as the reference voltage for the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# Table 1.9 Human machine interfaces (1 of 2)

| Feature                                 | Functional description                                      |

|-----------------------------------------|-------------------------------------------------------------|

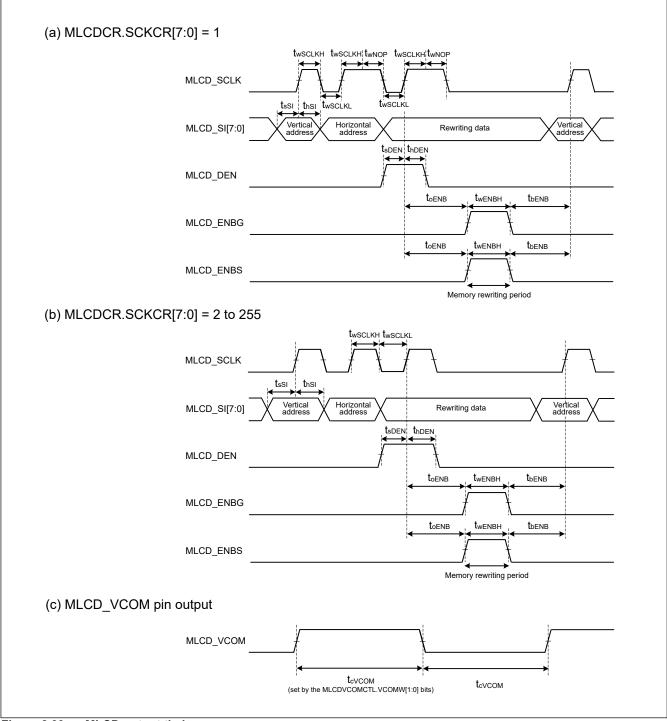

| MIP LCD controller (MLCD) <sup>*1</sup> | MIP-method liquid crystal panel driver circuit incorporated |

| Feature                                      | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2D graphics data conversion circuit<br>(GDT) | <ul> <li>A graphic accelerator circuit that handles 2D image processing incorporated</li> <li>Handling of up to 32-byte image data. Up to 63 × 64 bits for conversion of glyph data into image data.</li> <li>Rotations of 90-degree clockwise, 90-degree counterclockwise, vertical flip, and horizontal flip</li> <li>Scaling down to 1/8, 2/8, 3/8, 4/8, 5/8, 6/8, or 7/8 by pixel averaging and to 1/2 by pixel skipping</li> <li>Inversion allows bit-wise inversion of images; 1 is inverted to 0, and vice versa.</li> <li>Monochrome compositing of a foreground image, background image, and trimming image</li> <li>Color compositing of a foreground image and background image, and setting of priority color and transparent color</li> <li>Scrolling of an image in 1-bit units</li> <li>Conversion of glyph data into image data</li> <li>Colorization of monochrome images by RGB values</li> <li>Color data sorting allows separate R, G, and B images in memory to be sorted into a single area in order of R, G, and B</li> <li>Endian conversion</li> </ul> |

Note 1. General three-wire MIP can be supported by combining SPI0 and GDT.

# Table 1.10 Data processing

| Feature                                       | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Cyclic Redundancy Check (CRC)<br>calculator   | The Cyclic Redundancy Check (CRC) calculator generates CRC codes to detect errors in the data. The bit order of CRC calculation results can be switched for LSB-first or MSB-first communication. Additionally, various CRC-generation polynomials are available. The snoop function allows monitoring of reads from and writes to specific addresses. This function is useful in applications that require CRC code to be generated automatically in certain events, such as monitoring writes to the serial transmit buffer and reads from the serial receive buffer. |  |  |  |

| Data Operation Circuit (DOC)                  | The Data Operation Circuit (DOC) compares, adds, and subtracts 16-bit data. When a selected condition applies, 16-bit data is compared and an interrupt can be generated.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Divider (DIV)                                 | <ul> <li>A circuit for handling high-speed division for signed 32-bit fixed point data</li> <li>Dividend: Signed 32-bit data</li> <li>Divisor: Signed 32-bit data</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Data inversion and Logical operation<br>(DIL) | <ul> <li>Data inversion <ul> <li>The bit inversion value of input data is output</li> </ul> </li> <li>AND, OR, and XOR operations of two input data <ul> <li>Data inversion enables NAND, NOR, and XNOR operations</li> </ul> </li> <li>Conversion of data alignment per byte width (byte swap)</li> <li>Bit order inversion of MSB and LSB every 8 bits</li> </ul>                                                                                                                                                                                                     |  |  |  |

# Table 1.11 Security

| Feature                            | Functional description                                                                                                                                                                                                                                                             |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trusted Secure IP Lite (TSIP-Lite) | <ul> <li>Access management circuit available</li> <li>Security algorithms:         <ul> <li>Common key cryptosystem (symmetrical cryptography): AES key length: 128 bits/256 bits</li> <li>Encryption usage modes: GCM, ECB, CBC, CMAC, XTS, CTR, GCTR, CCM</li> </ul> </li> </ul> |

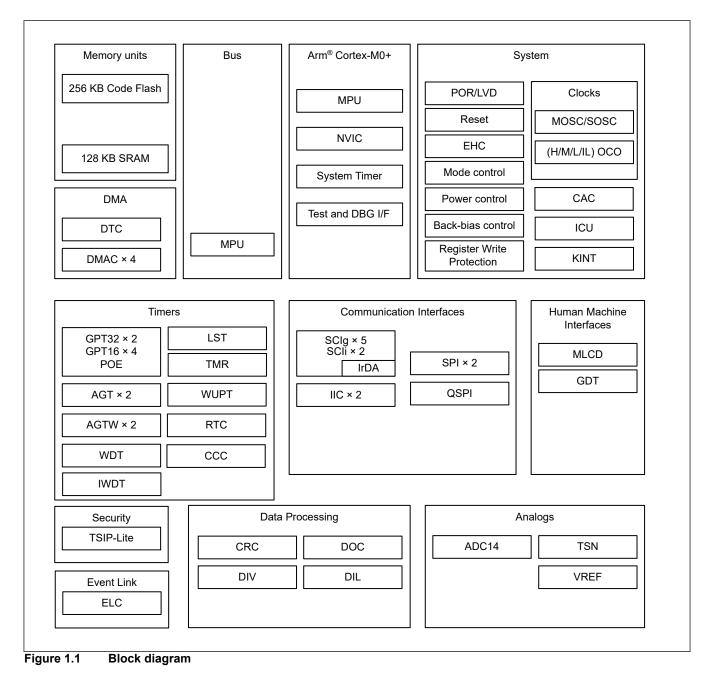

# 1.2 Block Diagram

Figure 1.1 shows a block diagram of the superset. Some individual devices within the group have a subset of the features.

# 1.3 Part Numbering

Table 1.12 shows a list of products.

# Table 1.12 Product list

| Product part number | Package code               | Code flash | SRAM      | TSIP-Lite     |

|---------------------|----------------------------|------------|-----------|---------------|

| R7F0E01182CFP       | PLQP0100KB-B 256 KB 128 KB |            | Supported |               |

| R7F0E01082CFP       | PLQP0100KB-B               |            |           | Not supported |

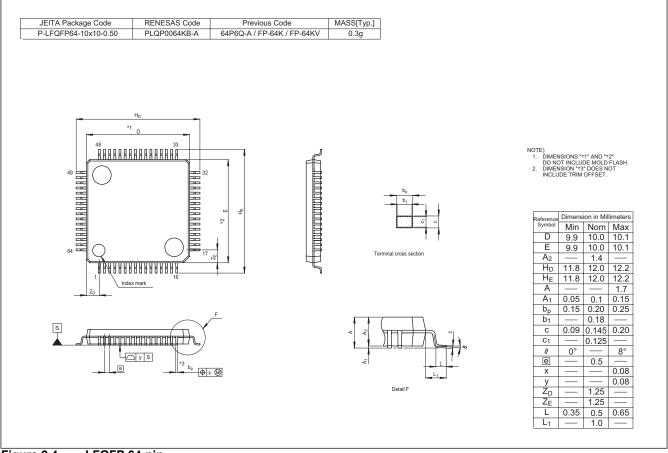

| R7F0E01182CFM       | PLQP0064KB-A               |            |           | Supported     |

| R7F0E01082CFM       | PLQP0064KB-A               |            |           | Not supported |

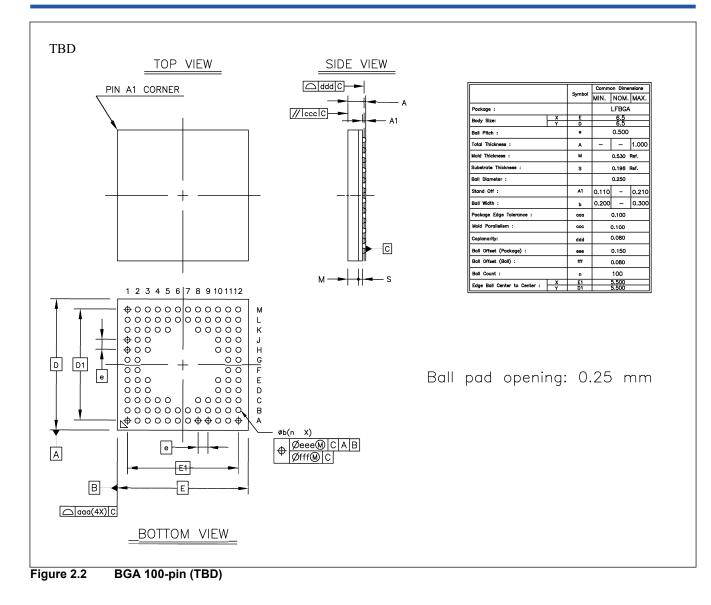

| R7F0E01182DBH       | TBD (BGA100pin)            |            |           | Supported     |

| R7F0E01082DBH       | TBD (BGA100pin)            |            |           | Not supported |

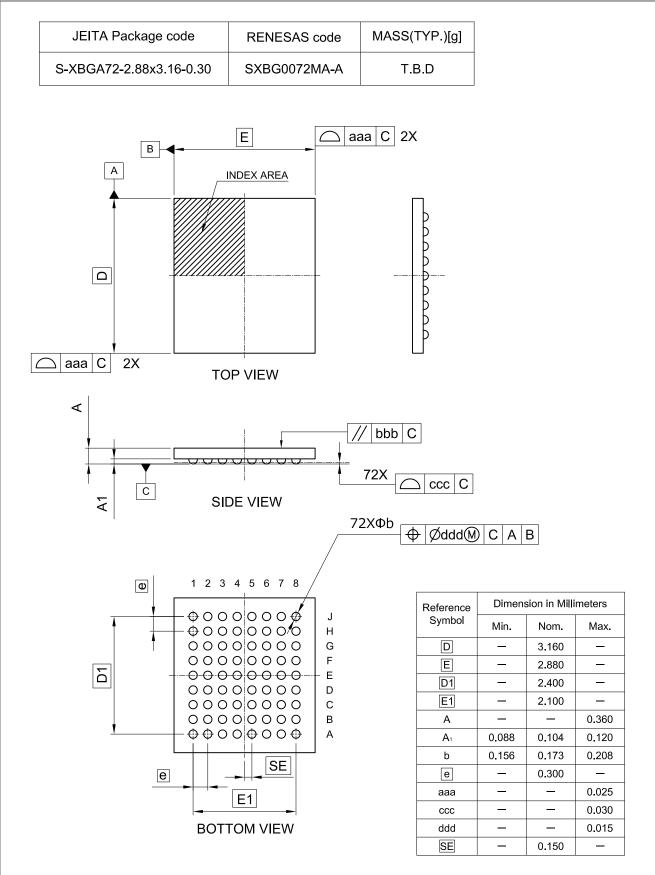

| R7F0E01182DBR       | SXBG0072MA-A               |            |           | Supported     |

| R7F0E01082DBR       | SXBG0072MA-A               |            |           | Not supported |

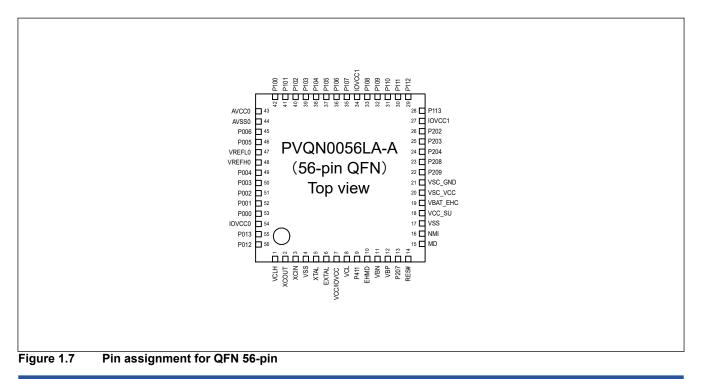

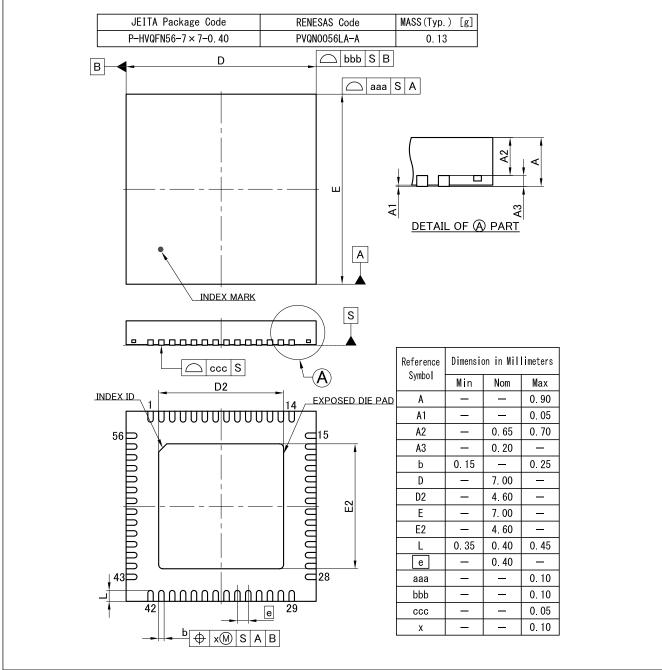

| R7F0E01182DNG       | PVQN0056LA-A               |            |           | Supported     |

| R7F0E01082DNG       | PVQN0056LA-A               |            |           | Not supported |

# 1.4 Function Comparison

# Table 1.13Function Comparison (1 of 4)

| Part Number            |          |                                                                                                              | R7F0E01182CFP   | R7F0E01082CFP | R7F0E01182CFM             | R7F0E01082CFM | R7F0E01182DBH | R7F0E01082DBH |

|------------------------|----------|--------------------------------------------------------------------------------------------------------------|-----------------|---------------|---------------------------|---------------|---------------|---------------|

| Pin count              |          | 100                                                                                                          |                 | 64            |                           | 100           |               |               |

| GPIO I/                | I/O pins |                                                                                                              | 73              |               | 3                         | 7             | 7             | 3             |

| Ir                     | nput pir | IS                                                                                                           |                 | 1             |                           | 1             |               | 1             |

| Package                |          |                                                                                                              |                 | LF            | QFP                       |               | В             | GA            |

| Code flash memory      | ,        |                                                                                                              |                 |               | 256                       | 6 KB          |               |               |

| SRAM                   |          |                                                                                                              |                 |               | 128                       | 8 KB          |               |               |

| CPU operating freqency |          | 32 MHz maximum (Normal mode)<br>64 MHz maximum (Boost mode)<br>32.768 kHz maximum (Low leakage current mode) |                 |               |                           |               |               |               |

| Interrupt control      |          | ICU                                                                                                          | Yes             |               |                           |               |               |               |

|                        |          | IRQ                                                                                                          | Channe          | els 0 to 9    | Channels 0 to 5, 7, and 8 |               | Channe        | ls 0 to 9     |

| Key interrupt          |          | KINT                                                                                                         |                 |               | 8 cha                     | nnels         |               |               |

| DMA                    |          | DTC                                                                                                          | Yes             |               |                           |               |               |               |

| DMAC                   |          |                                                                                                              | Channels 0 to 3 |               |                           |               |               |               |

| Event control          |          | ELC                                                                                                          | Yes             |               |                           |               |               |               |

| Energy harvesting      |          | EHC                                                                                                          | Yes             |               |                           |               |               |               |

| Back-bias voltage c    | ontrol   | VBBC                                                                                                         | Yes             |               |                           |               |               |               |

| Part Number     |          |                    | R7F0E01182CFP                           | R7F0E01082CFP | R7F0E01182CFM | R7F0E01082CFM | R7F0E01182DBH | R7F0E01082DBH |  |  |

|-----------------|----------|--------------------|-----------------------------------------|---------------|---------------|---------------|---------------|---------------|--|--|

| Timers          | GPT32    |                    | Channels 0 and 1                        |               |               |               |               |               |  |  |

|                 | GPT16    |                    | Channels 2 to 5                         |               |               |               |               |               |  |  |

|                 |          | POE                |                                         |               | Y             | es            |               |               |  |  |

|                 | AGT      | 1                  |                                         |               | Channel       | s 0 and 1     |               |               |  |  |

|                 | AGTW     |                    |                                         |               | Channel       | s 0 and 1     |               |               |  |  |

|                 | TMR      |                    |                                         |               | Channel       | s 0 and 1     |               |               |  |  |

|                 | WUPT     |                    |                                         |               | Y             | es            |               |               |  |  |

|                 | RTC      |                    |                                         |               | Y             | es            |               |               |  |  |

|                 | CCC      |                    |                                         |               | Y             | es            |               |               |  |  |

|                 | WDT      |                    |                                         |               | Y             | es            |               |               |  |  |

|                 | IWDT     |                    |                                         |               | Y             | es            |               |               |  |  |

|                 | LST      |                    |                                         |               | Y             | es            |               |               |  |  |

| Communications  | SClg     | w/o FIFO           |                                         |               | Channels 2    | 2 to 5, and 9 |               |               |  |  |

|                 | SCli     | w/ FIFO            | Channels 0 and 1                        |               |               |               |               |               |  |  |

|                 |          | IrDA               | Yes                                     |               |               |               |               |               |  |  |

|                 | IIC      |                    | Channels 0 and 1 Channel 1 Channels 0 a |               |               |               | s 0 and 1     |               |  |  |

|                 | SPI      | 128 bit buffer     |                                         | Channel 0     |               |               |               |               |  |  |

|                 |          | 32 bit buffer      | Channel 1                               |               |               |               |               |               |  |  |

|                 | QSPI     | -                  | Yes                                     |               |               |               |               |               |  |  |

| Analogs         | ADC14    | High precision     | 8 channels                              |               |               |               |               |               |  |  |

|                 |          | Standard precision | 4 cha                                   | innels        | Ν             | lo            | 4 cha         | innels        |  |  |

|                 | TSN      |                    | Yes                                     |               |               |               |               |               |  |  |

|                 | VREF     |                    | Yes                                     |               |               |               |               |               |  |  |

| HMI graphics    | MLCD     |                    | Yes                                     |               |               |               |               |               |  |  |

|                 | GDT      |                    | Yes                                     |               |               |               |               |               |  |  |

| Data Processing | CRC      |                    | Yes                                     |               |               |               |               |               |  |  |

|                 | DOC      |                    | Yes                                     |               |               |               |               |               |  |  |

|                 | DIV      |                    | Yes                                     |               |               |               |               |               |  |  |

|                 | DIL      |                    | Yes                                     |               |               |               |               |               |  |  |

| Security        | TSIP-Lit | te                 | Yes                                     | No            | Yes           | No            | Yes           | No            |  |  |

### Table 1.13Function Comparison (2 of 4)

# Table 1.13 Function Comparison (3 of 4)

| Function               |            | R7F0E01182DBR                                                                                                | R7F0E01082DBR | R7F0E01182DNG | R7F0E01082DNG |  |

|------------------------|------------|--------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|--|

| Pin count              |            | 7                                                                                                            | 72            |               | 6             |  |

| GPIO I/O pins          |            | 4                                                                                                            | 3             | 33            |               |  |

|                        | Input pins |                                                                                                              | 1             | 1             |               |  |

| Package                |            | WL                                                                                                           | BGA           | QFN           |               |  |

| Code flash mer         | nory       | 256 KB                                                                                                       |               |               |               |  |

| SRAM                   |            | 128 KB                                                                                                       |               |               |               |  |

| CPU operating freqency |            | 32 MHz maximum (Normal mode)<br>64 MHz maximum (Boost mode)<br>32.768 kHz maximum (Low leakage current mode) |               |               | e)            |  |

| Function          |         |                    | R7F0E01182DBR                                    | R7F0E01082DBR | R7F0E01182DNG | R7F0E01082DNG |  |

|-------------------|---------|--------------------|--------------------------------------------------|---------------|---------------|---------------|--|

| Interrupt control |         | ICU                |                                                  |               | Yes           |               |  |

|                   |         | IRQ                | Channels 0 to 9 Channels 0 to 5, Channels 7 to 8 |               |               |               |  |

| Key interrupt     |         | KINT               | 8 channels                                       |               |               |               |  |

| DMA               |         | DTC                | Yes                                              |               |               |               |  |

|                   |         | DMAC               |                                                  | Chan          | nels 0 to 3   |               |  |

| Event control     |         | ELC                |                                                  |               | Yes           |               |  |

| Energy harvesting | 9       | EHC                |                                                  |               | Yes           |               |  |

| Back-bias voltage | control | VBBC               |                                                  |               | Yes           |               |  |

| Timers            | GPT32   |                    |                                                  | Chann         | els 0 and 1   |               |  |

|                   | GPT16   |                    |                                                  | Chan          | nels 2 to 5   |               |  |

|                   |         | POE                |                                                  |               | Yes           |               |  |

|                   | AGT     |                    |                                                  | Chann         | els 0 and 1   |               |  |

|                   | AGTW    |                    |                                                  | Chann         | els 0 and 1   |               |  |

|                   | TMR     |                    |                                                  | Chann         | els 0 and 1   |               |  |

|                   | WUPT    |                    |                                                  |               | Yes           |               |  |

|                   | RTC     |                    |                                                  |               | Yes           |               |  |

|                   | CCC     |                    | Yes                                              |               |               |               |  |

|                   | WDT     |                    | Yes                                              |               |               |               |  |

|                   | IWDT    |                    | Yes                                              |               |               |               |  |

|                   | LST     |                    | Yes                                              |               |               |               |  |

| Communications    | SClg    | w/o FIFO           | Channels 2 to 5, and 9                           |               |               |               |  |

|                   | SCli    | w/ FIFO            |                                                  | Chann         | els 0 and 1   |               |  |

|                   |         | IrDA               |                                                  | Yes           |               |               |  |

|                   | IIC     |                    | Channels                                         | s 0 and 1     | Char          | nnel 1        |  |

|                   | SPI     | 128 bit buffer     |                                                  | Ch            | annel 0       |               |  |

|                   |         | 32 bit buffer      |                                                  | Ch            | annel 1       |               |  |

|                   | QSPI    |                    |                                                  |               | Yes           |               |  |

| Analogs           | ADC14   | High precision     |                                                  | 8 c           | hannels       |               |  |

|                   |         | Standard precision | 4 cha                                            | nnels         | N             | lo            |  |

|                   | TSN     |                    | Yes                                              |               |               |               |  |

|                   | VREF    |                    | Yes                                              |               |               |               |  |

| HMI graphics      |         |                    | Yes                                              |               |               |               |  |

|                   | GDT     |                    | Yes                                              |               |               |               |  |

| Data Processing   | CRC     |                    | Yes                                              |               |               |               |  |

|                   | DOC     |                    |                                                  |               | Yes           |               |  |

| DIV               |         |                    |                                                  |               | Yes           |               |  |

#### Table 1.13 Function Comparison (4 of 4)

DIL

Security

TSIP-Lite

No

Yes

Yes

Yes

No

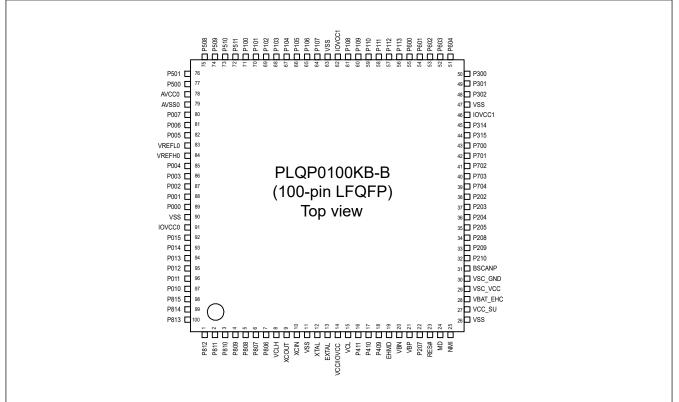

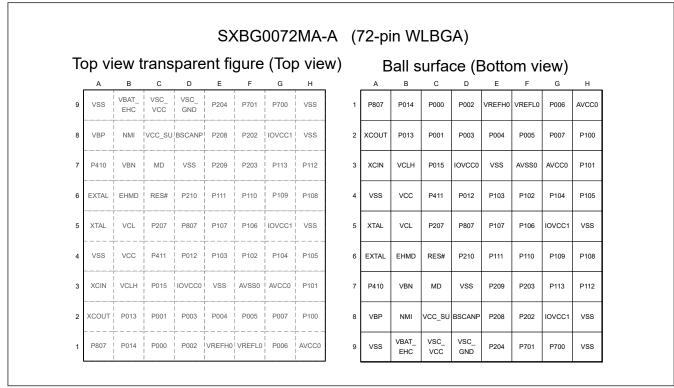

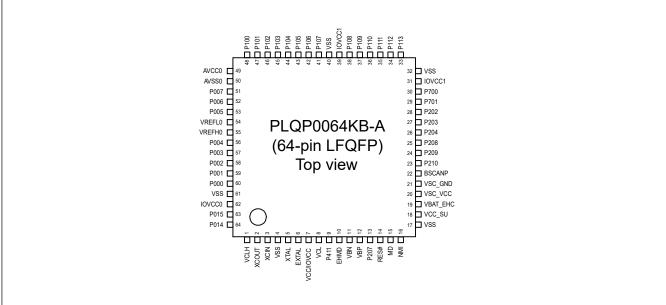

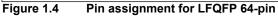

# 1.5 Pin Functions

Table 1.14 shows a list of pin functions.

# Table 1.14Pin functions (1 of 6)

| Function     | Signal     | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

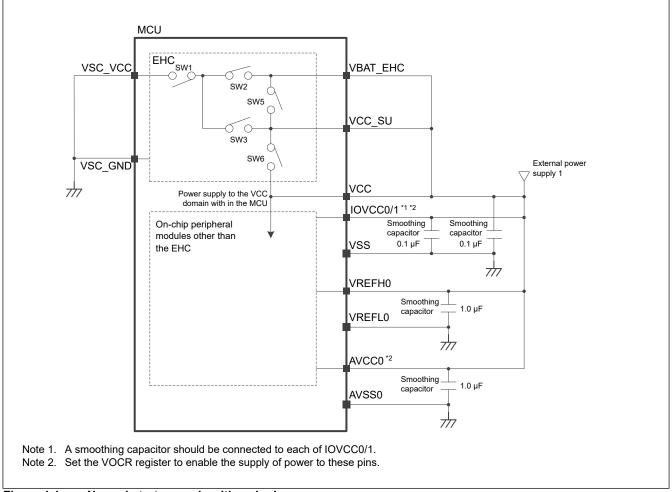

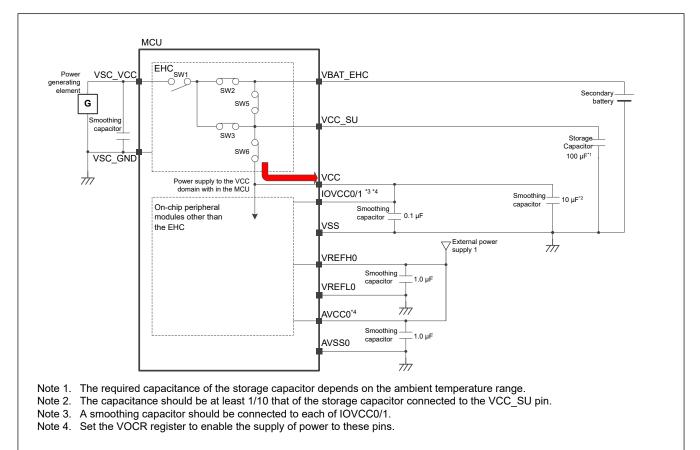

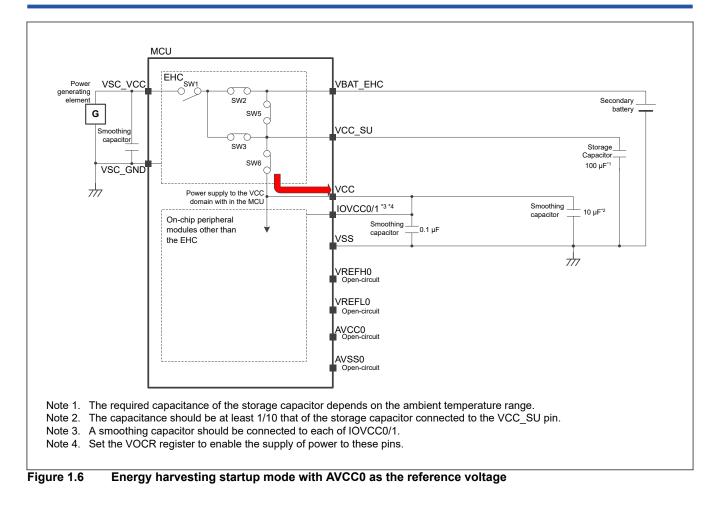

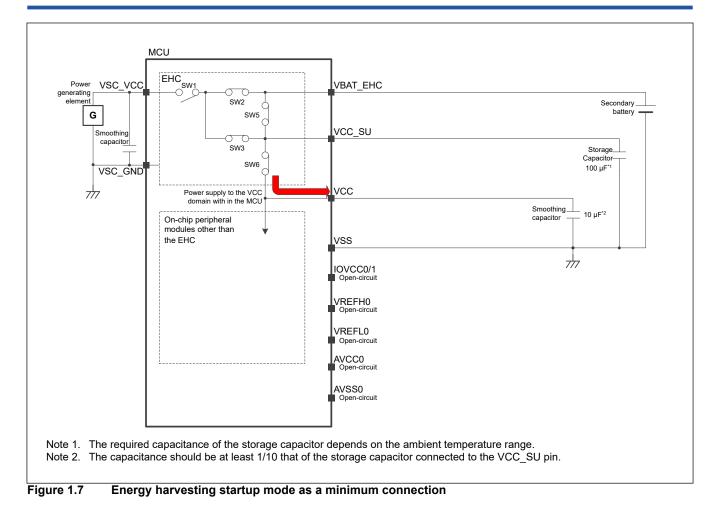

| Power supply | VCC/ IOVCC | Input | <ul> <li>Normal startup mode         Power supply pin. Connect it to the system power supply.<br/>Connect to VSS through a 0.1-μF smoothing capacitor. Place<br/>the smoothing capacitor close to the pin.*<sup>2</sup> Apply voltage prior<br/>to the IOVCCn pins.     </li> <li>Energy harvesting startup mode         Power supply pin. Connect it to the system power supply.<br/>Connect to VSS through 0.1-μF smoothing capacitor (1). Place<br/>the smoothing capacitor close to the pin.<br/>In addition, connect to VSS through smoothing capacitor (2)<br/>having capacity of 1/10 of capacity of a storage capacitor<br/>connected to the VCC_SU pin to improve robustness against<br/>external noise and obtain stable operation of the circuit. For<br/>instance, connect a 4.7-μF smoothing capacitor in the case<br/>where a 47-μF storage capacitor is connected to the VCC_SU<br/>pin.<br/>If placing the smoothing capacitor (2) close to this pin is<br/>possible, the smoothing capacitor (1) is not required.     </li> </ul> |

|              | VSS        | Input | Ground pin. Connect it to the system power supply (0 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              | VCL        | Input | Internal power supply stabilization pin. Connect the pin to VSS through a $4.7$ - $\mu$ F smoothing capacitor. Place the smoothing capacitor close to the pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              | VCLH       | Input | Internal power supply stabilization pin. Separately from the VCL pin, connect the VCLH pin to VSS through a 4.7- $\mu$ F smoothing capacitor. Place the smoothing capacitor close to the pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

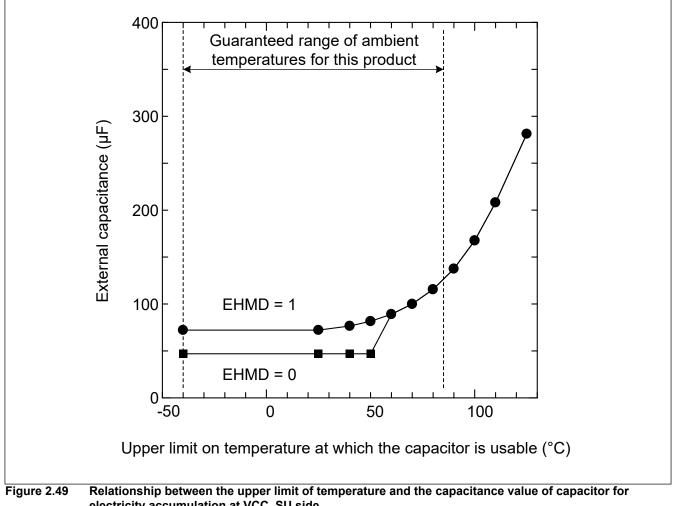

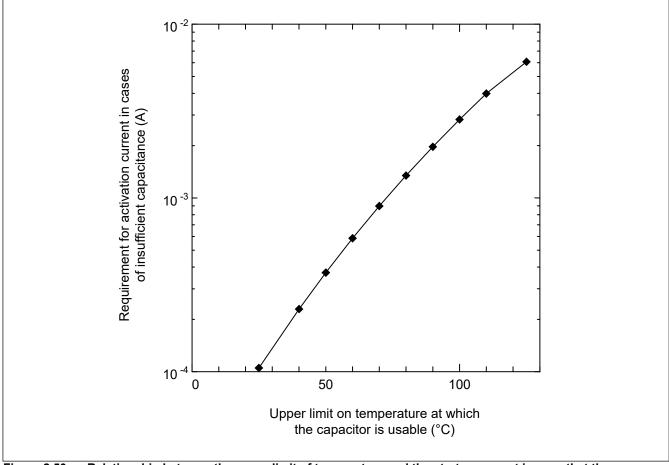

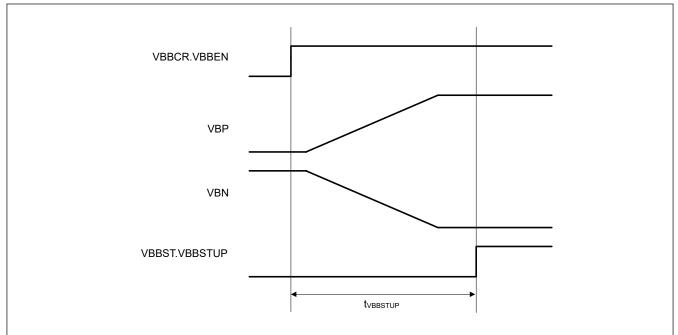

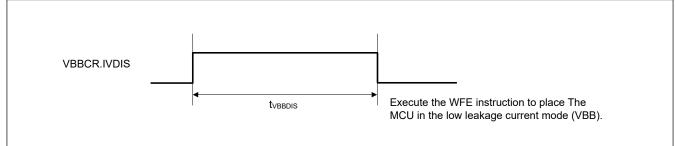

|              | VBN        | _     | Back-bias voltage stabilization pin. Connect the pin to VSS through                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |