### PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

#### **General Description**

The MAX20360 is a highly integrated and programmable power management solution designed for ultra-low-power wearable applications. It is optimized for size and efficiency to enhance the value of the end product by extending battery life and shrinking the overall solution size. A flexible set of power-optimized voltage regulators, including multiple buck, boost and buck-boost converters, and linear regulators, provides a high level of integration and the ability to create a fully optimized power architecture. The quiescent current of each regulator is ultra-low targeted at extending battery life in always-on applications.

The MAX20360 includes a complete battery management solution with battery seal, charger, power path, and fuel gauge. Both thermal management and input protection are built into the charger. The device also includes a factory programmable button controller with multiple inputs that are customizable to fit specific product UX requirements.

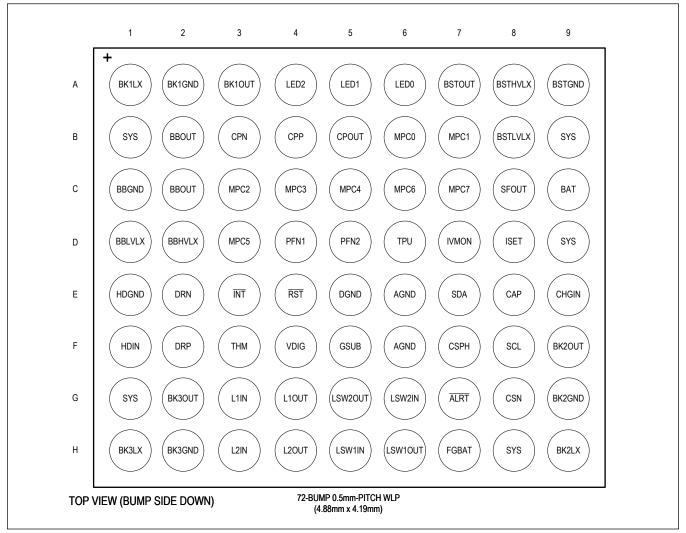

Three integrated LED current sinks are included for indicator or backlighting functions, and an ERM/LRA driver with automatic resonance tracking is capable of providing sophisticated haptic feedback to the user. A low noise, 1.5W buck-boost converter provides a clean way to power LEDs commonly used in optical heart-rate systems. The device is configurable through an I<sup>2</sup>C interface that allows for programming various functions and reading the device status, including the ability to read temperature and supply voltages with the integrated ADC. This device is available in a 72-bump, 0.5mm pitch, 4.88mm x 4.19mm, wafer-level package (WLP) and operates over the -40°C to +85°C extended temperature range.

### **Applications**

- Wearable Devices

- IoT

#### **Benefits and Features**

- Extend Battery-Use Time Between Battery Charging

2 x Micro-I<sub>Q</sub>, 400mA Buck Regulators (330nA I<sub>Q</sub> typ each)

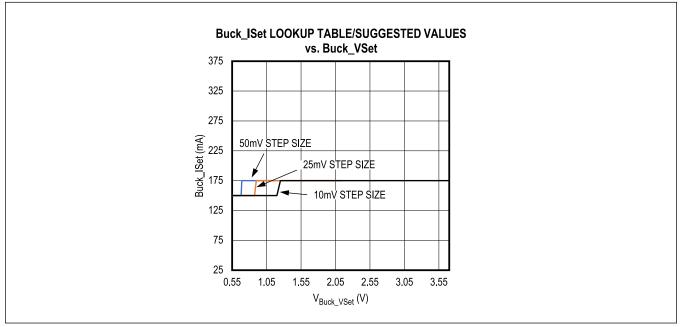

- 0.550V to 1.180V in 10mV Steps

- 0.550V to 2.125V in 25mV Steps

- 0.550V to 3.700V in 50mV Steps

- Micro-I<sub>Q</sub>, 600mA Buck Regulator (330nA I<sub>Q</sub> typ)

- 0.550V to 1.180V in 10mV Steps

- 0.550V to 2.125V in 25mV Steps

- 0.550V to 3.700V in 50mV Steps

- Micro-I<sub>Q</sub> LV LDO/Load Switch (1µA I<sub>Q</sub> typ)

- 1.0V to 2.0V Input Voltage

- 50mA Output

- 0.5V to 1.95V Output, 25mV Steps

- Micro-I<sub>Q</sub> LDO/Load Switch (1µA I<sub>Q</sub> typ)

- 1.71V to 5.5V Input Voltage

- 100mA Output

- 0.9V to 4V, 100mV Steps

- Micro-I<sub>O</sub> Buck-Boost Regulator (2µA I<sub>O</sub> typ)

- 1.5W Output

- · 2.6V to 5V in 50mV Steps

- Easy-to-Implement Li+ Battery Charging

- Wide Fast Charge Current Range: 5mA to 500mA

- 28V/-5.5V Tolerant Input

- Programmable JEITA Current/Voltage Profiles

- Minimize Solution Footprint through High Integration

- 3.3V or 5.0V Safe Output LDO

- 15mA When CHGIN Present

- ERM/LRA Haptic Driver

- Automatic Braking (LRA Only)

- Automatic Resonance Tracking (LRA only)

- Supports a Wide Variety of Display Options

- Micro-I<sub>Q</sub> Boost Regulator (2.4µA I<sub>Q</sub> typ)

- 300mW Output

- 5V to 20V in 250mV Steps

- 3-Channel Current Sinks

- 20V Tolerant

- Programmable from 0.6mA to 30mA

- Optimize System Control

- Programmable Push-Button Controller

- Programmable Supply Sequencing

- Factory Shelf Mode

- On-Chip Voltage/Charge Current Monitor Mux and Analog-to-Digital Converter (ADC)

Ordering Information appears at end of data sheet.

## PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

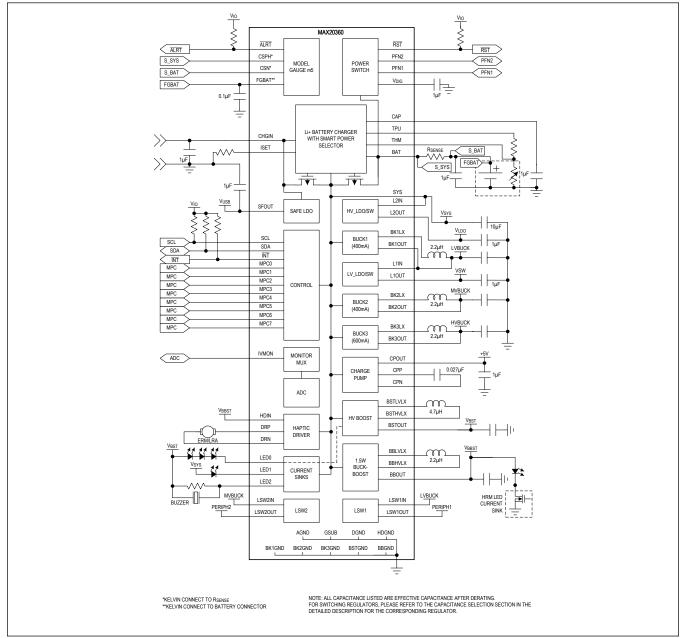

### Simplified Block Diagram

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

### TABLE OF CONTENTS

| General Description                            | . 1 |

|------------------------------------------------|-----|

| Applications                                   | . 1 |

| Benefits and Features                          | . 1 |

| Simplified Block Diagram                       | . 2 |

| Absolute Maximum Ratings                       | . 9 |

| Package Information                            | . 9 |

| 72 WLP                                         | . 9 |

| Electrical Characteristics                     | . 9 |

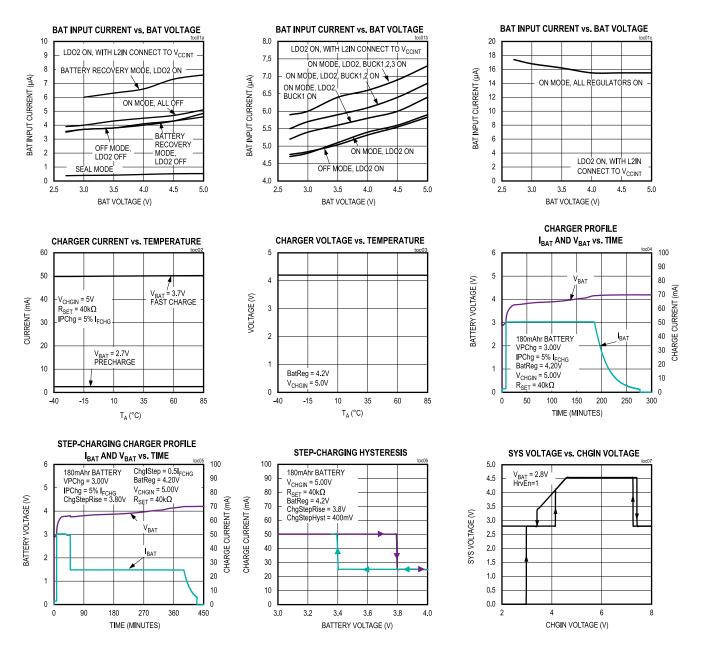

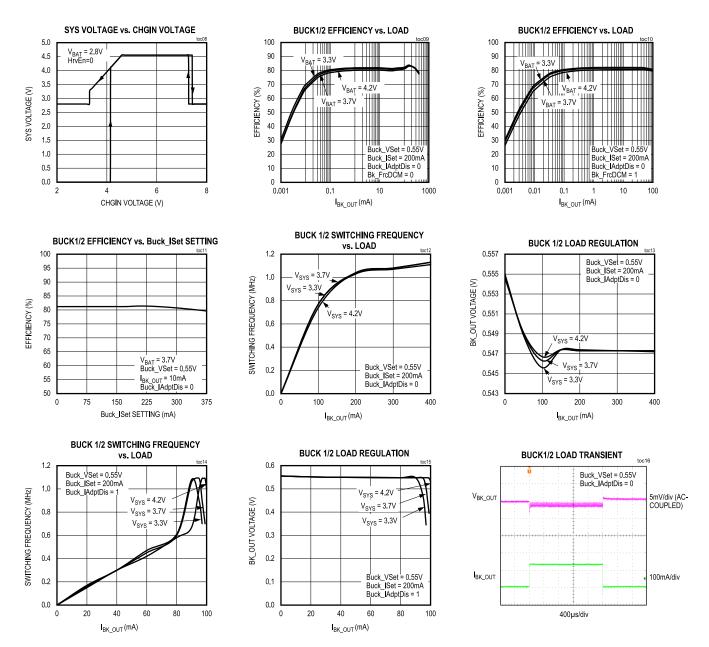

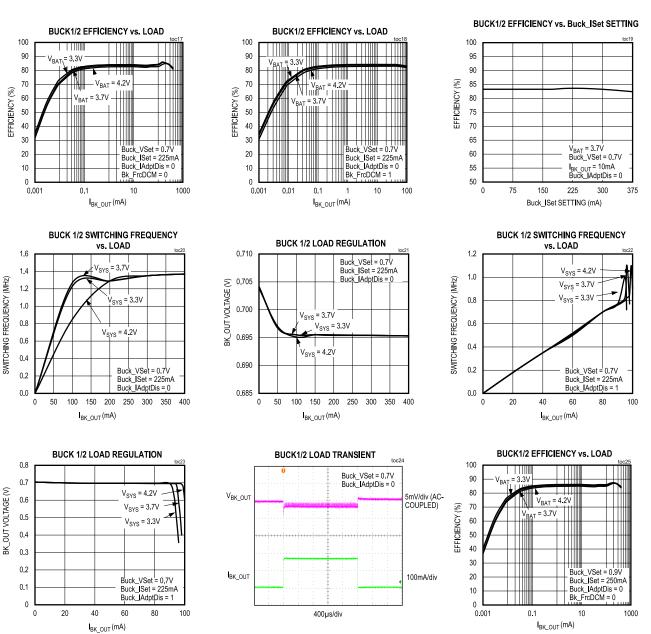

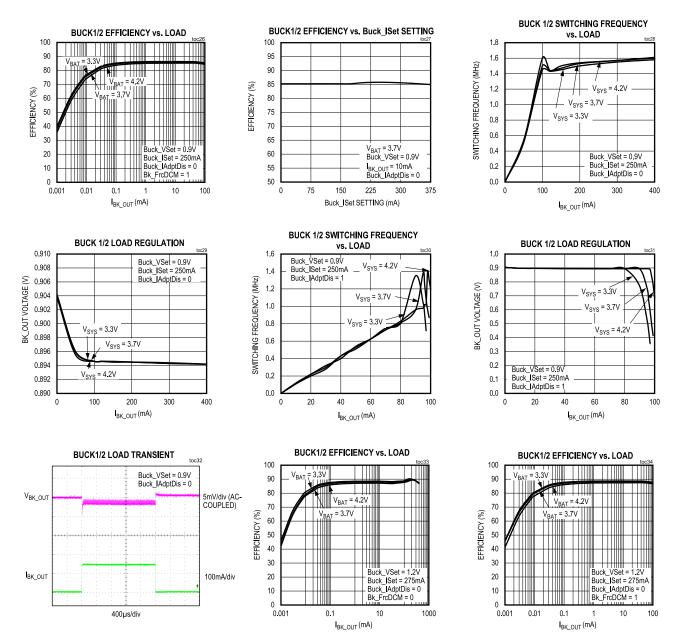

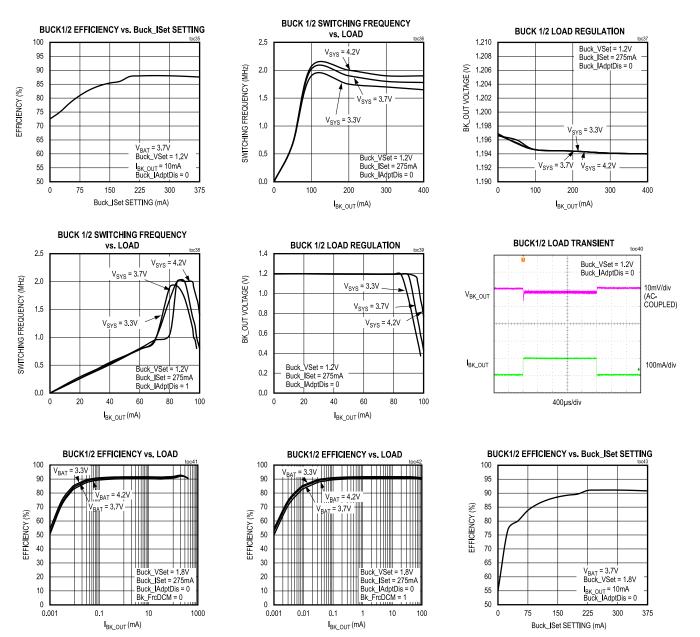

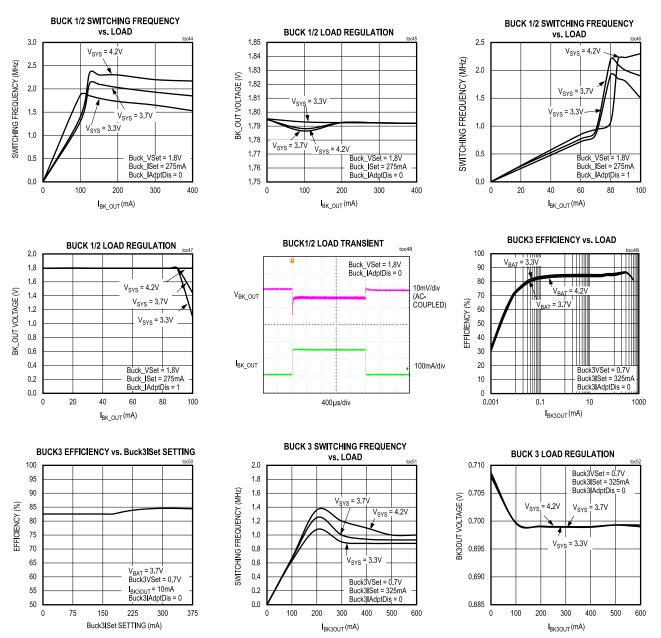

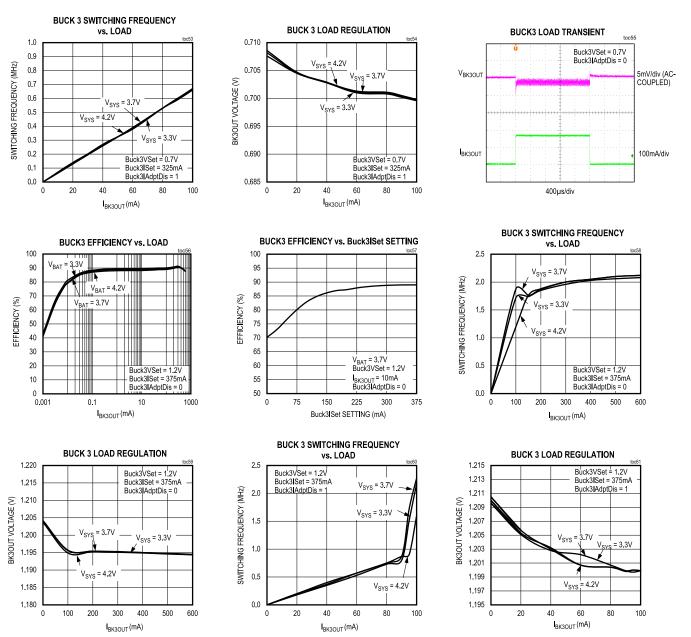

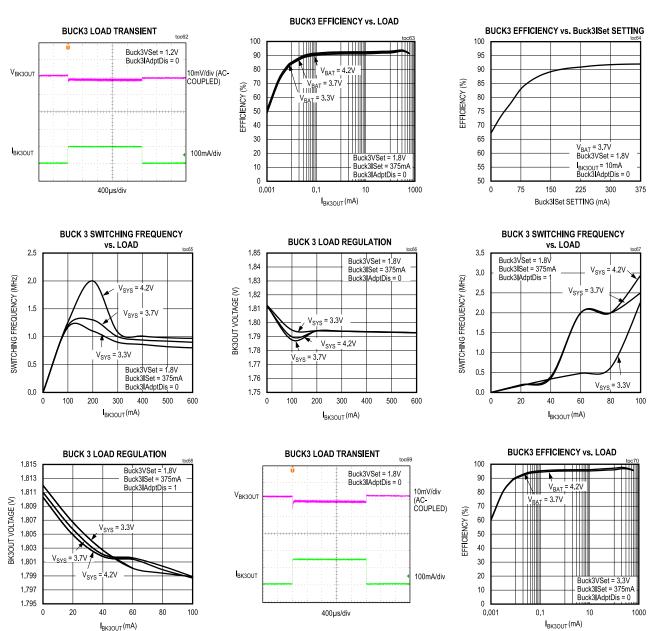

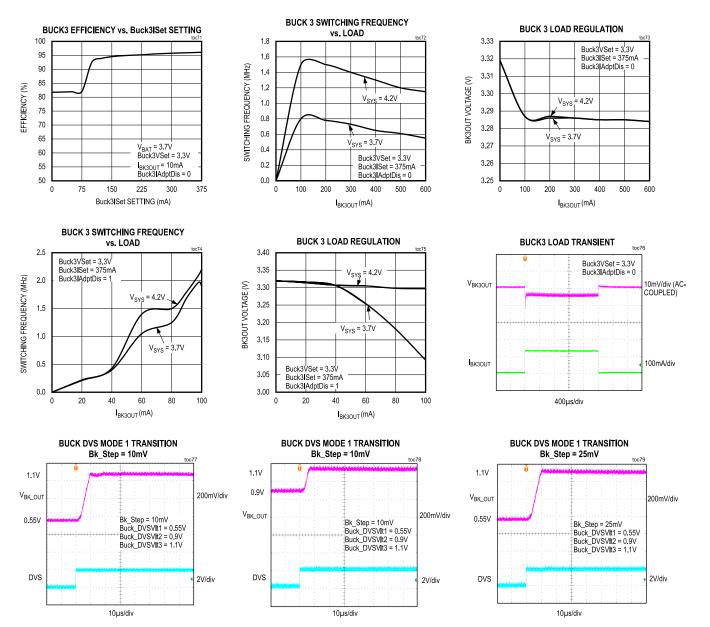

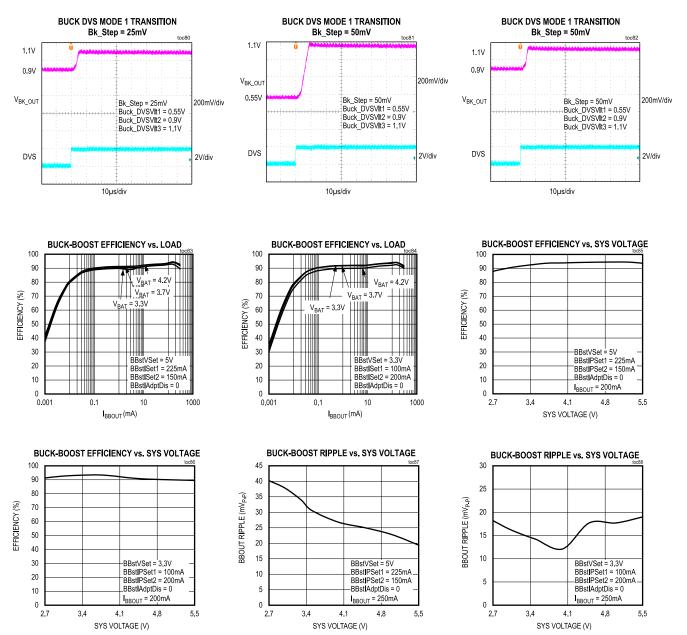

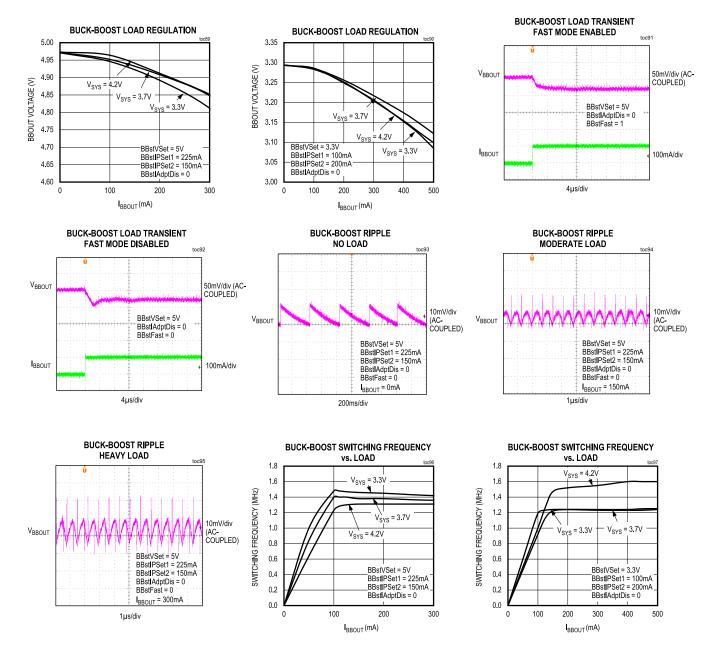

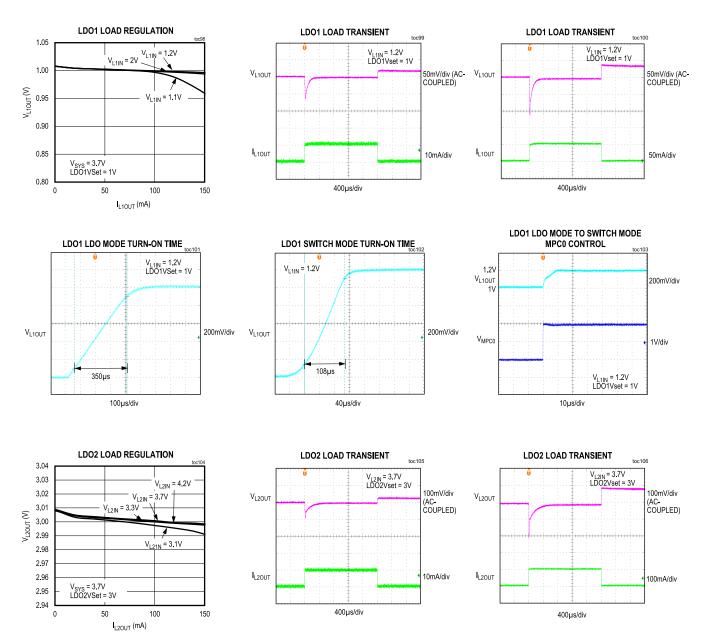

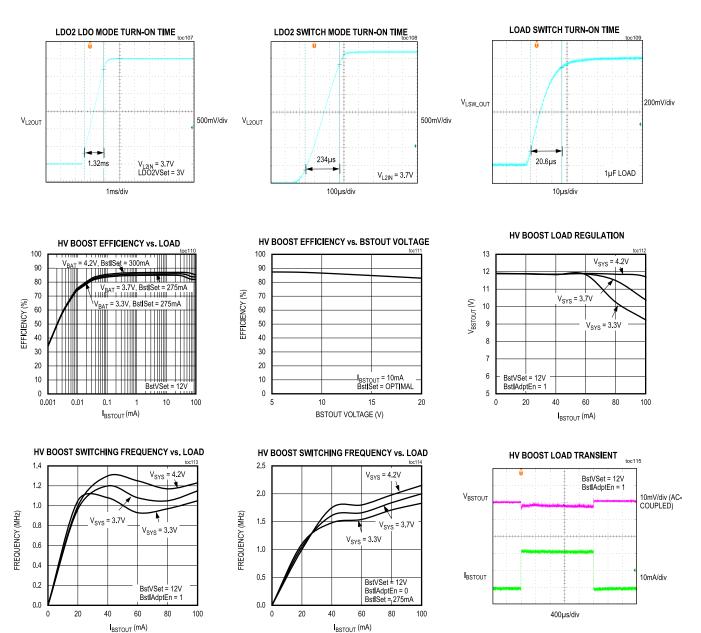

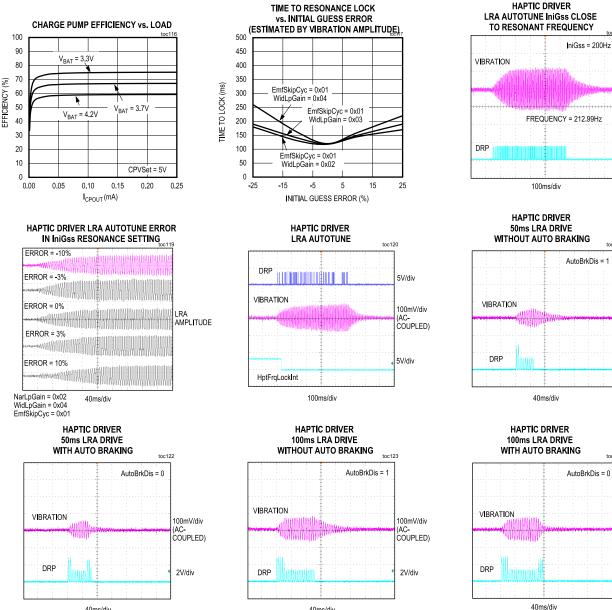

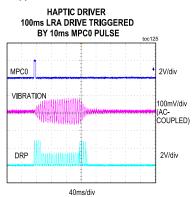

| Typical Operating Characteristics              | 37  |

| Pin Configuration                              | 53  |

| MAX20360                                       | 53  |

| Pin Description                                | 53  |

| Detailed Description                           | 56  |

| Power Regulation                               | 56  |

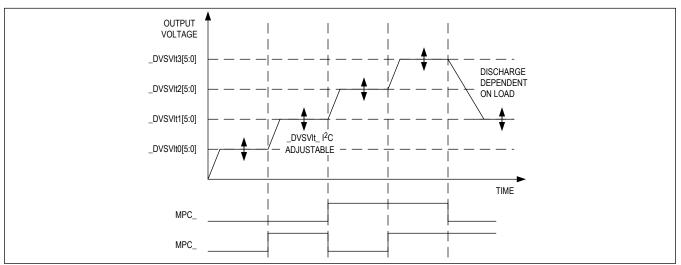

| Dynamic Voltage Scaling                        | 56  |

| DVS Mode 0 (I <sup>2</sup> C DVS Mode)         | 56  |

| DVS Mode 1 (GPIO DVS Mode)                     | 56  |

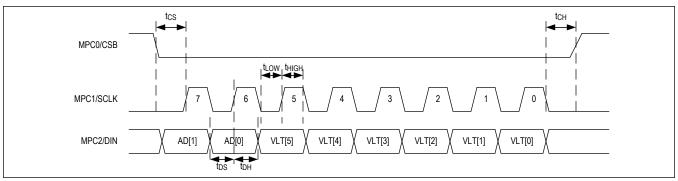

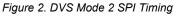

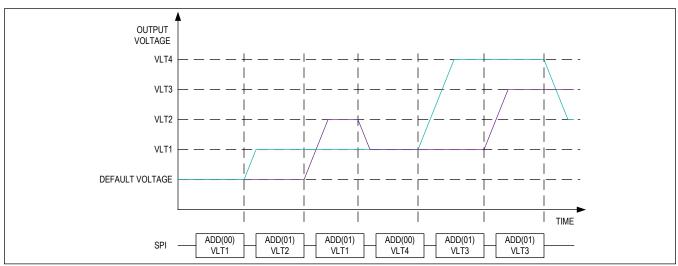

| SPI DVS Mode (DVS Mode 2)                      | 57  |

| Dedicated DVS Interrupts.                      | 58  |

| Buck Converter DVS Options                     | 59  |

| LDOs                                           | 59  |

| LDO Output Capacitance Selection               | 59  |

| LDO1 MPC0 Control                              | 59  |

| Internal Switchover for LDO2 Always-On Power   | 59  |

| Load Switches                                  | 59  |

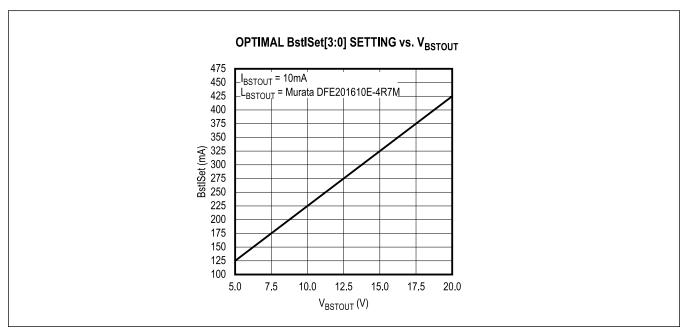

| Boost Regulator                                | 60  |

| Boost Inductor Selection                       | 60  |

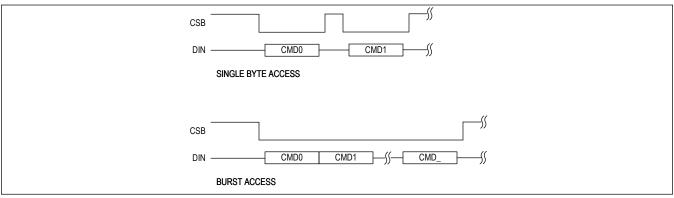

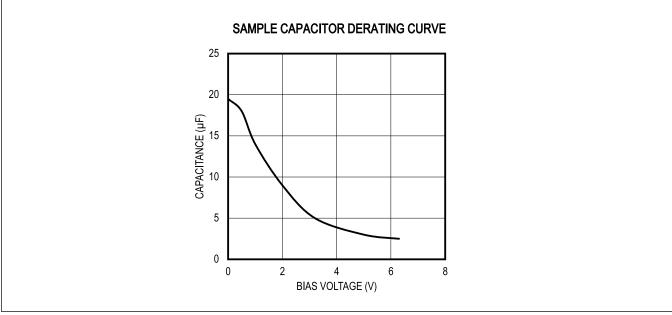

| Boost Capacitor Selection                      | 61  |

| Inductor Peak Current Limit                    | 61  |

| Boost Converter and LED0 Closed Loop Operation | 62  |

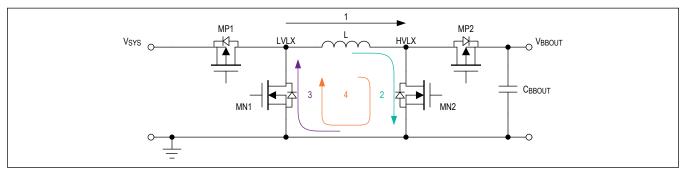

| Buck-Boost Regulator                           | 62  |

| Buck-Boost Inductor Selection                  | 62  |

| Buck-Boost Output Capacitor Selection          | 63  |

| Architecture and Switching Phases              | 63  |

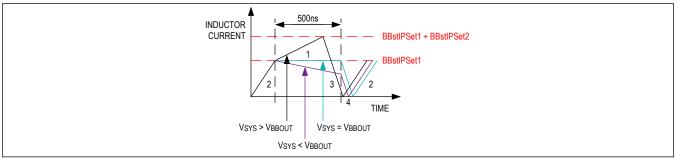

| Buck-Boost Mode                                | 64  |

| Buck-Only Mode.                                |     |

| Inductor Peak and Valley Current Limits        |     |

| Buck Regulators                                |     |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

### **TABLE OF CONTENTS (CONTINUED)**

| Buck Inductor Selection                            | 67 |

|----------------------------------------------------|----|

| Buck Output Capacitor Selection                    | 67 |

| Inductor Peak and Valley Current Limits            | 68 |

| Adjustments to Manipulate Buck Switching Frequency | 68 |

| High Power Buck Converter with LDO Mode            | 69 |

| Charge Pump                                        | 69 |

| Power Switch and Reset Control                     | 69 |

| PMIC Power Modes                                   | 82 |

| SEAL Mode                                          | 82 |

| OFF Mode                                           | 82 |

| ON Mode (Versions with HrvEn = 0)                  | 82 |

| Battery Recovery Mode (Versions with HrvEn = 1)    | 82 |

| ON Mode (Versions with HrvEn = 1)                  | 82 |

| Power Sequencing                                   | 82 |

| System Load Switch                                 | 85 |

| Smart Power Selector                               | 86 |

| Input Limiter                                      | 86 |

| Invalid CHGIN Voltage Protection                   | 86 |

| CHGIN Input Current Limit                          | 86 |

| Thermal Limiting                                   | 86 |

| Battery Charger                                    | 86 |

| Adaptive Battery Charging                          | 86 |

| Fast Charge Current Setting                        | 86 |

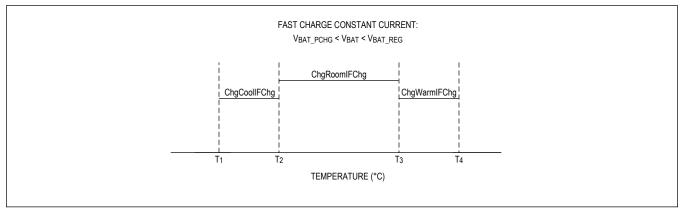

| JEITA Monitoring with Charger Control              | 87 |

| Step Charging                                      | 88 |

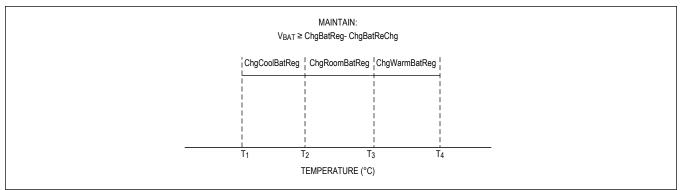

| Battery Charger State Diagram                      | 88 |

| Battery or Pack Protector Presence Detection       | 89 |

| SAR ADC/Monitor Mux                                | 90 |

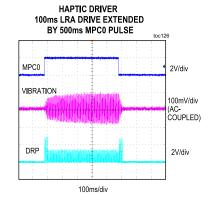

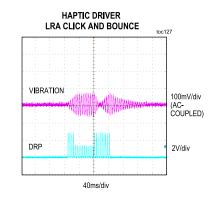

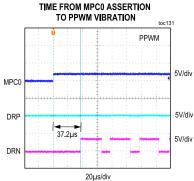

| Haptic Driver                                      | 91 |

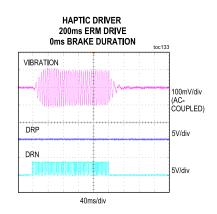

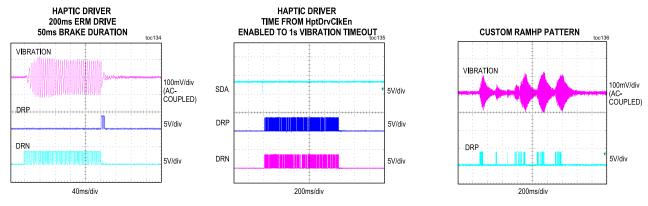

| Eccentric Rotating Mass (ERM)                      | 91 |

| Linear Resonant Actuator (LRA)                     | 91 |

| LRA Braking                                        | 91 |

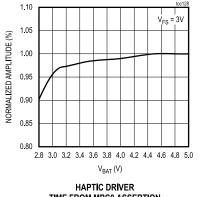

| Automatic Level Compensation                       | 92 |

| Haptic UVLO                                        | 92 |

| Driver Amplitude                                   | 92 |

| Vibration Timeout                                  | 92 |

| Overcurrent/Thermal Protection                     | 92 |

| Haptic Driver Lock                                 | 92 |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

### **TABLE OF CONTENTS (CONTINUED)**

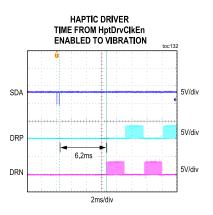

| Interface Modes.                                     | 93 |

|------------------------------------------------------|----|

| Pure-PWM (PPWM)                                      | 93 |

| Real-Time I <sup>2</sup> C (RTI <sup>2</sup> C).     | 93 |

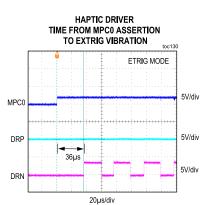

| External Triggered Stored Pattern (ETRG)             | 93 |

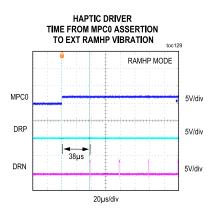

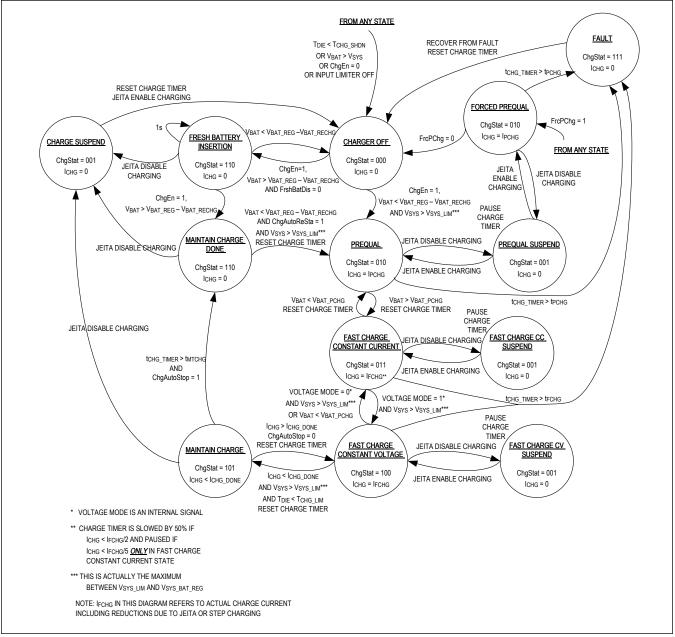

| RAM Stored Haptic Pattern (RAMHP)                    | 93 |

| Fuel Gauge                                           | 96 |

| MAX20361 Harvester Interaction                       | 96 |

| Harvester Thermistor Monitoring                      | 97 |

| Register Map                                         | 98 |

| Haptic Driver and ADC Registers - SlaveID: 0xA0/0xA1 | 98 |

| Register Details                                     | 00 |

| PMIC Registers - SlaveID: 0x50/0x51 1                | 17 |

| Register Details                                     | 22 |

| Applications Information                             | 91 |

| I <sup>2</sup> C Interface                           | 91 |

| Start, Stop, and Repeated Start Conditions 1         | 91 |

| Slave Address                                        | 91 |

| Bit Transfer                                         | 91 |

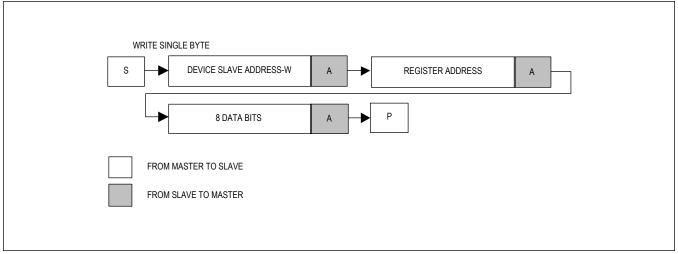

| Single-Byte Write                                    | 91 |

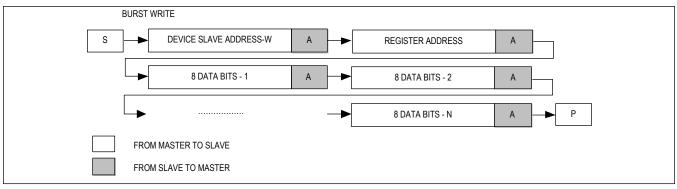

| Burst Write                                          | 92 |

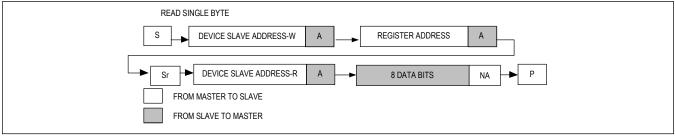

| Single Byte Read.                                    | 93 |

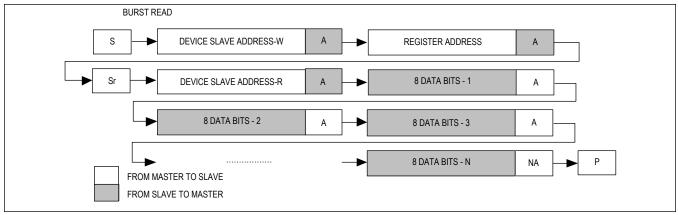

| Burst Read                                           | 93 |

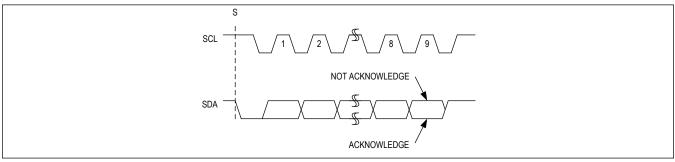

| Acknowledge Bits                                     | 94 |

| I <sup>2</sup> C Security Functions                  | 94 |

| Function Locking                                     | 94 |

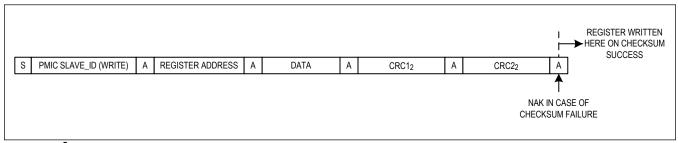

| Secure Writes with Fletcher-16 Checksum 1            | 94 |

| Default Bits                                         | 95 |

| Register Defaults                                    | 98 |

| Ordering Information                                 | 02 |

| Revision History                                     | 03 |

## PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

#### **LIST OF FIGURES**

| Figure 1. DVS Mode 1, GPIO Control                                              | 57  |

|---------------------------------------------------------------------------------|-----|

| Figure 2. DVS Mode 2 SPI Timing                                                 | 58  |

| Figure 3. DVS Mode 2, SPI Control                                               | 58  |

| Figure 4. Single-Byte and Burst-Mode SPI Access                                 | 58  |

| Figure 5. Minimum Effective Capacitance for HVBOOST Stability                   | 60  |

| Figure 6. Optimal Peak Current vs. Voltage Lookup Table                         | 61  |

| Figure 7. Buck-Boost Required Minimum Output Capacitance                        | 63  |

| Figure 8. The Buck-Boost Regulator and Switching Phases                         | 64  |

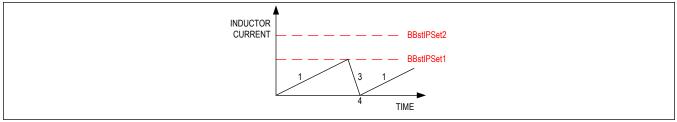

| Figure 9. Buck-Boost Inductor Current in Buck-Boost Mode                        | 64  |

| Figure 10. Buck-Boost Inductor Current in Buck-Only Mode                        | 65  |

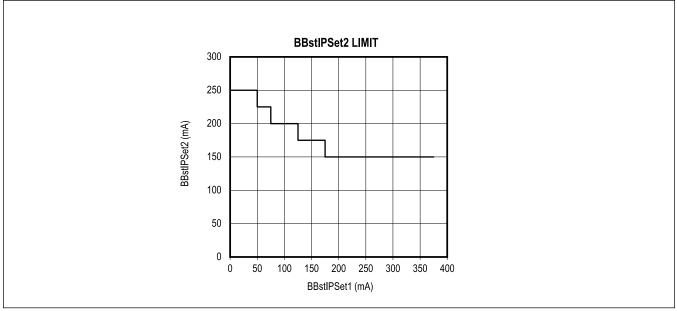

| Figure 11. Minimum BBstIPSet2 Limit for a Given BBstIPSet1 Setting              | 66  |

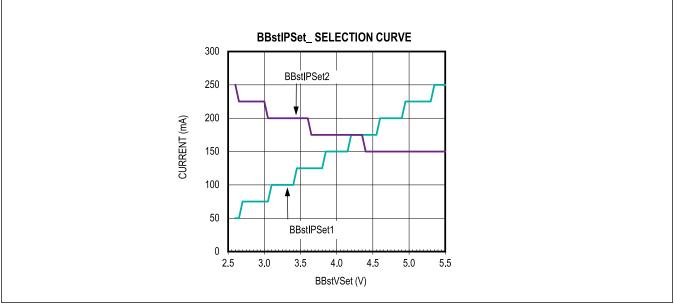

| Figure 12. Recommended BBstIPSet1 and BBstIPSet2 Settings                       | 66  |

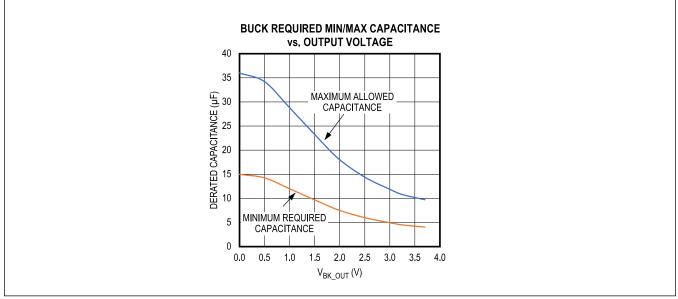

| Figure 13. Buck Required Minimum and Maximum Capacitance to Guarantee Stability | 67  |

| Figure 14. Optimal Peak Current Setting vs. Output Voltage                      | 68  |

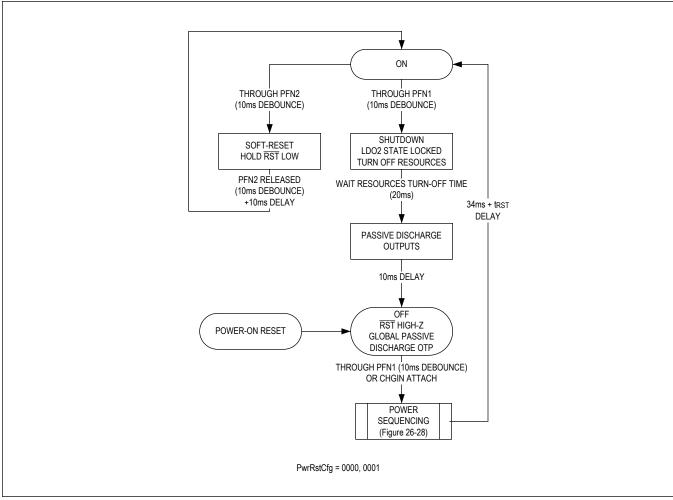

| Figure 15. PwrRstCfg 0000, 0001                                                 | 70  |

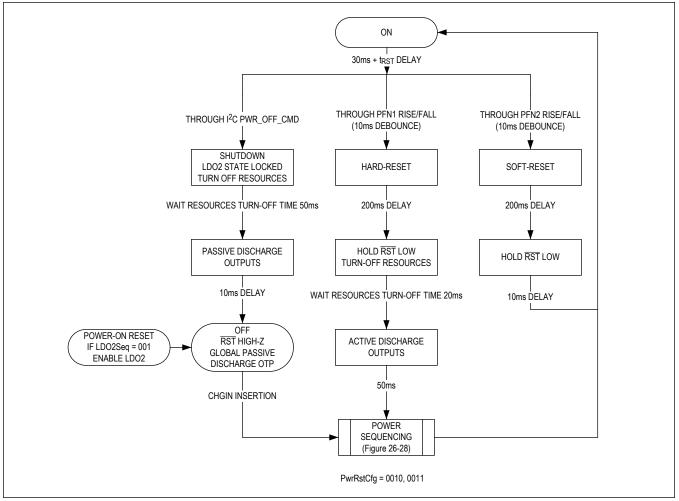

| Figure 16. PwrRstCfg 0010, 0011                                                 | 71  |

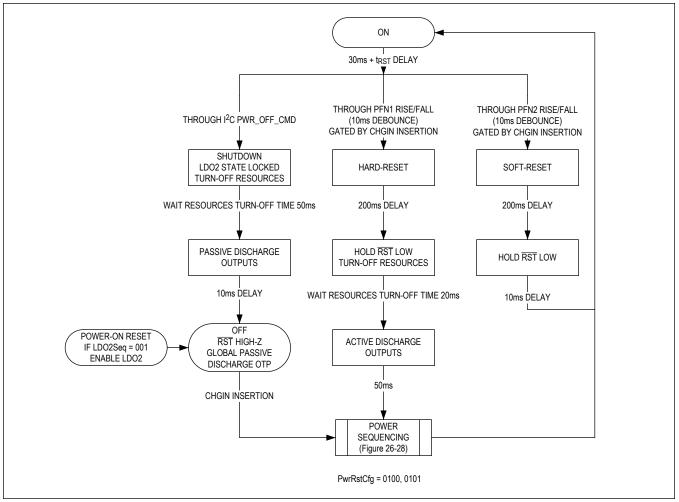

| Figure 17. PwrRstCfg 0100, 0101                                                 | 72  |

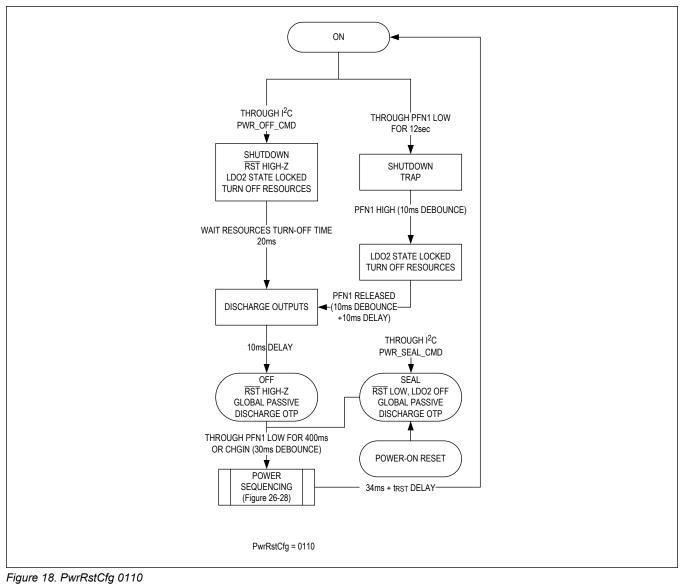

| Figure 18. PwrRstCfg 0110                                                       | 73  |

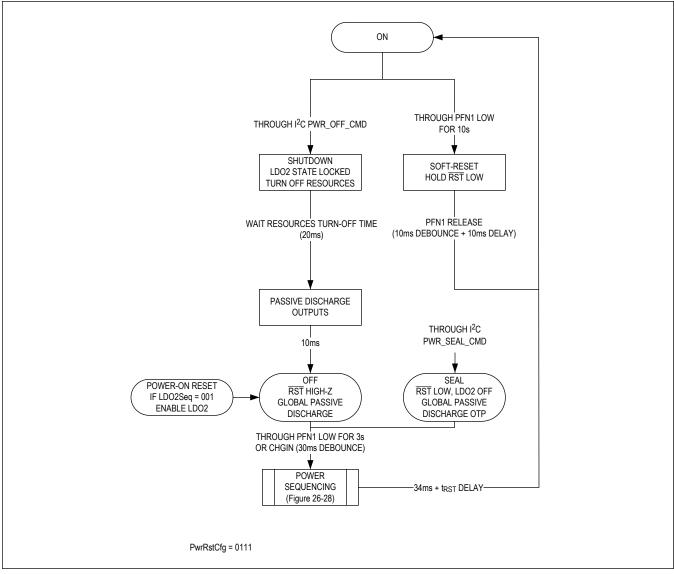

| Figure 19. PwrRstCfg 0111                                                       | 74  |

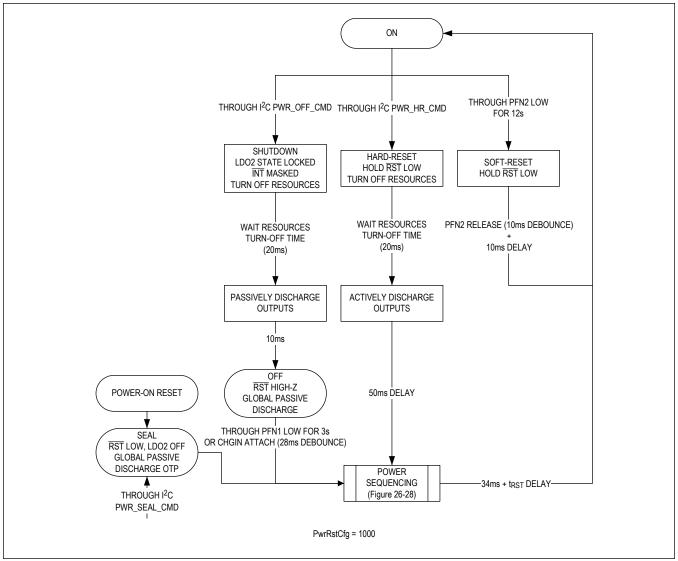

| Figure 20. PwrRstCfg 1000                                                       | 75  |

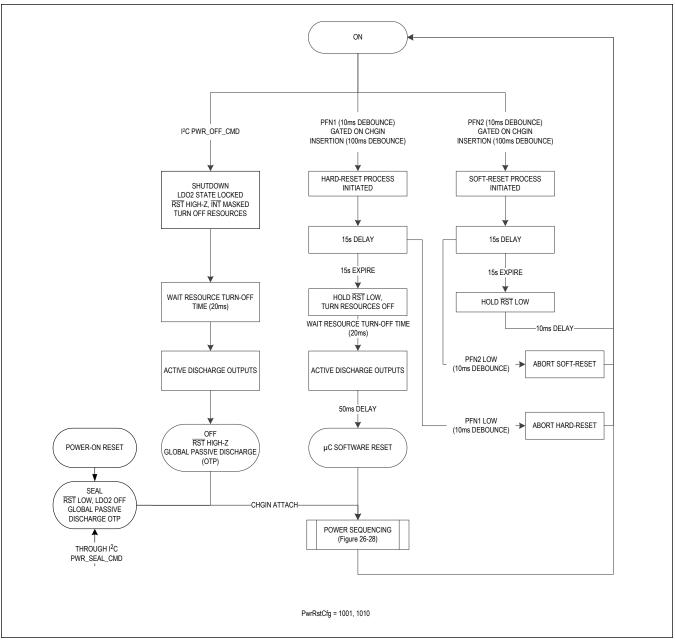

| Figure 21. PwrRstCfg 1001, 1010                                                 | 76  |

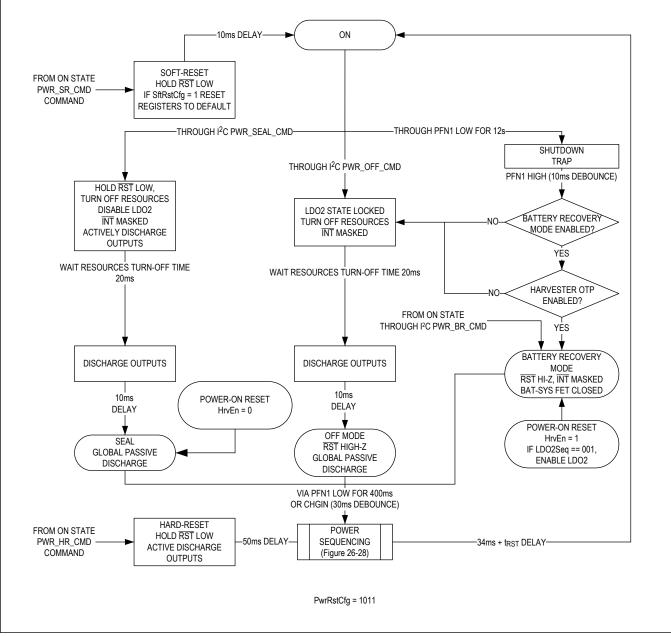

| Figure 22. PwrRstCfg 1011                                                       | 77  |

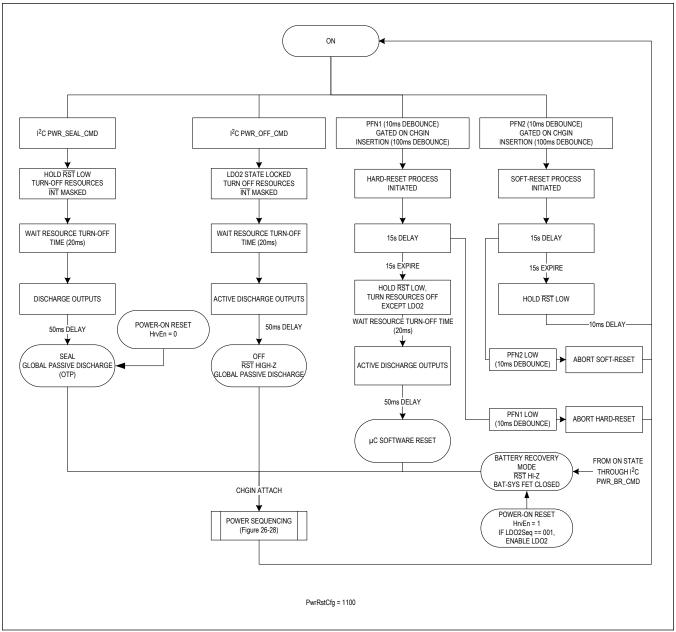

| Figure 23. PwrRstCfg 1100                                                       | 78  |

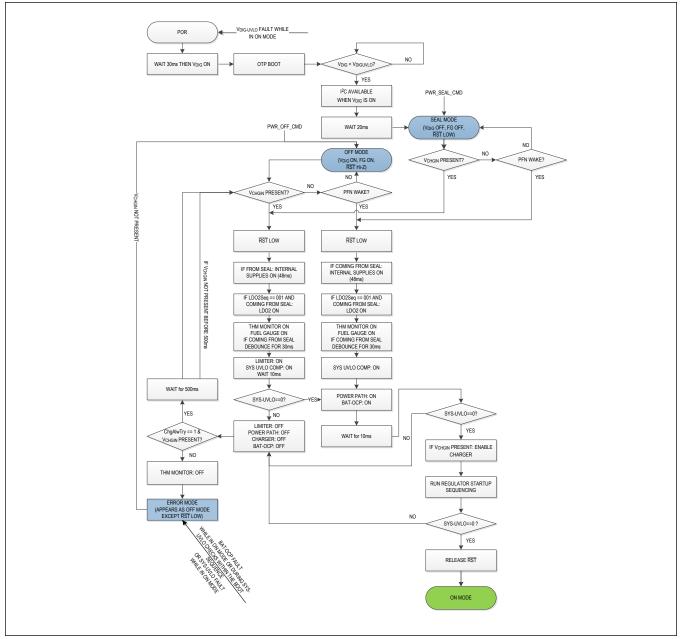

| Figure 24. Boot Sequence—Harvester Mode Disabled                                |     |

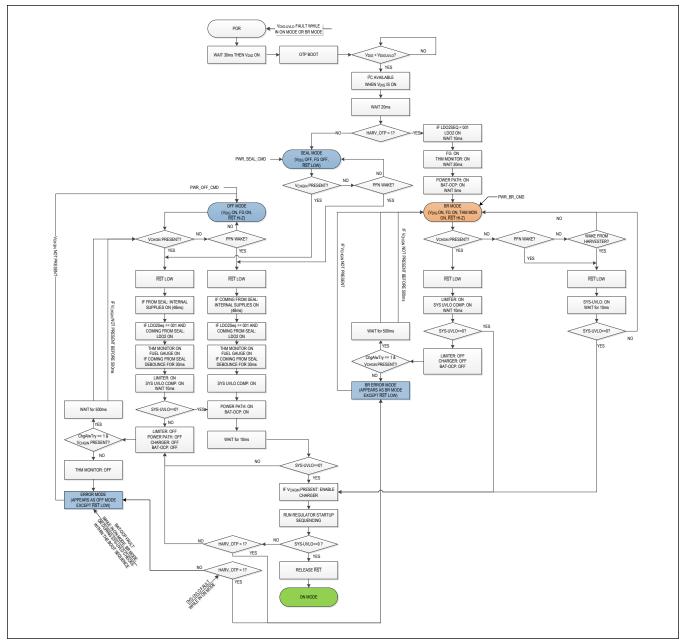

| Figure 25. Boot Sequence—Harvester Mode Enabled                                 | 81  |

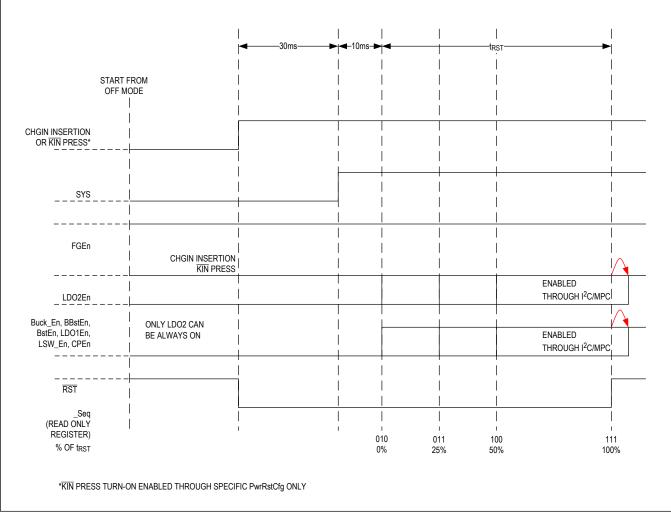

| Figure 26. Power Sequencing, HrvEn = 0 from OFF Mode                            | 83  |

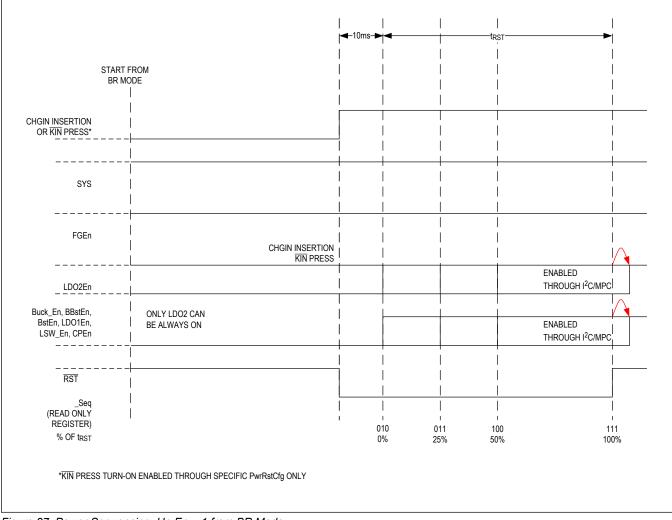

| Figure 27. Power Sequencing, HrvEn = 1 from BR Mode                             | 84  |

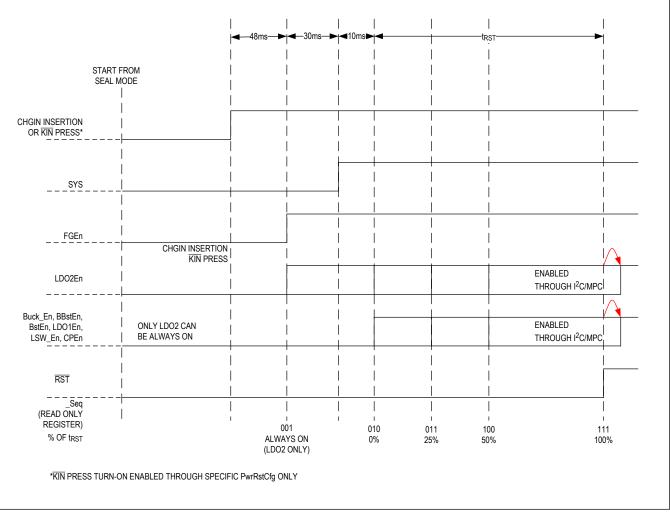

| Figure 28. Power Sequencing, from SEAL Mode                                     |     |

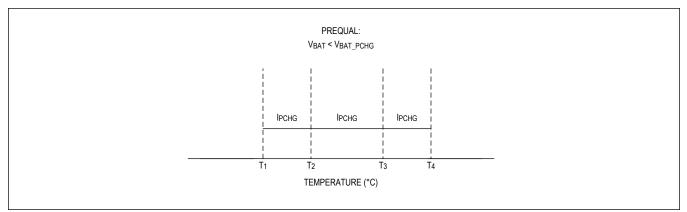

| Figure 29. Sample JEITA Pre-Charge Profile                                      | 87  |

| Figure 30. Sample JEITA Fast Charge Profile                                     | 87  |

| Figure 31. Sample JEITA Maintain Charge Profile                                 | 88  |

| Figure 32. Battery Charger-State Diagram                                        | 89  |

| Figure 33. Read and Write Process for Haptic RAM                                | 94  |

| Figure 34. Sample Pattern Stored in RAM                                         | 96  |

| Figure 35. Diagram of Haptic Driver Output for Sample Pattern Stored Pattern    | 96  |

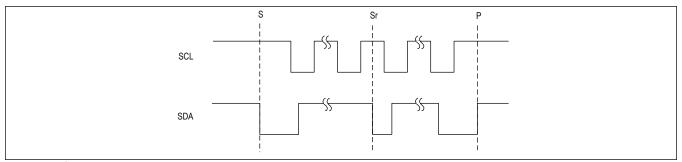

| Figure 36. I <sup>2</sup> C START, STOP, and REPEATED START Conditions          | 191 |

| Figure 37. Write Byte Sequence                                                  | 192 |

| Figure 38. Burst Write Sequence                                                 | 192 |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

### LIST OF FIGURES (CONTINUED)

| Figure 39. Read Byte Sequence                                                      | 193 |

|------------------------------------------------------------------------------------|-----|

| Figure 40. Burst Read Sequence                                                     | 194 |

| Figure 41. Acknowledge Bits.                                                       | 194 |

| Figure 42. I <sup>2</sup> C Writes on PMIC Slave Address with Fletcher-16 Checksum | 195 |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

#### LIST OF TABLES

| Table 1. DVS Mode 1 Voltage Selection              | . 57 |

|----------------------------------------------------|------|

| Table 2. LDO1 MPC0 Control                         | . 59 |

| Table 3. Recommended Inductors                     | . 63 |

| Table 4. Recommended Inductors Buck                | . 67 |

| Table 5. PwrRstCfg Settings                        | . 78 |

| Table 6. ADC Full-Scale Range                      | . 91 |

| Table 7. RAMHP Pattern Storage Format.             | . 94 |

| Table 8. Device Default Settings                   | 195  |

| Table 9. I <sup>2</sup> C Direct Register Defaults | 198  |

## PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

#### **Absolute Maximum Ratings**

| (All voltages referenced to GSUB, unless otherwise noted)         CHGIN       -6.0V to +30.0V         SYS, BAT, SDA, SCL, TPU, IVMON, RST, INT, PFN_, HDIN,         L2IN, LSW_IN, BBOUT, FGBAT       -0.3V to +6.0V         THM       -0.3V to min(V <sub>FGBAT</sub> + 0.3V, +6.0V)         ALRT       -0.3V to min(IV <sub>CHGIN</sub>   + 0.3V, +6.0V)         L1IN, VDIG       -0.3V to min(IV <sub>CHGIN</sub>   + 0.3V, +6.0V)         L1IN, VDIG       -0.3V to min(IV <sub>CHGIN</sub>   + 0.3V, +6.0V)         L1N, VDIG       -0.3V to +2.2V         MPC_, BK_LX, BK_OUT, BBLVLX, BSTLVLX, CPN       -0.3V to         (V <sub>SYS</sub> + 0.3V)       -0.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BSTHVLX, BSTOUT, LED0.3V to +22.0V<br>BK_GND, BSTGND, BBGND, HDGND, AGND, DGND0.3V to<br>+0.3V<br>CSN, CSPH                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $eq:spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_$ | Continuous Current into Any Other Terminal±100mA<br>Continuous Power Dissipation (Multilayer Board) ( $T_A = +70^{\circ}C$ ,<br>derate 32.53mW/°C above +70°C.)2602mW<br>Operating Temperature Range |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 72 WLP

| Package Code                           | W724A4+1                       |  |  |  |

|----------------------------------------|--------------------------------|--|--|--|

| Outline Number                         | <u>21-100373</u>               |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                                |  |  |  |

| Junction-to-Ambient (0 <sub>JA</sub> ) | 30.74°C/W                      |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/</u> <u>thermal-tutorial</u>.

#### **Electrical Characteristics**

| PARAMETER           | SYMBOL | CONDITIONS                                                                                                                                    | MIN | TYP  | MAX | UNITS |

|---------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| GLOBAL SUPPLY CURF  | RENT   |                                                                                                                                               |     |      |     |       |

| CHGIN Input Current | ICHGIN | V <sub>CHGIN</sub> = 5V, ON mode, Charger<br>disabled, THM monitoring disabled,<br>SFOUT disabled, LDO2 disabled, all<br>other rails disabled |     | 0.81 |     | mA    |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

### **Electrical Characteristics (continued)**

| PARAMETER                                                | SYMBOL                  | CONDITIONS                                                                                                                                                            | MIN  | TYP  | MAX  | UNITS |  |

|----------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

|                                                          |                         | V <sub>CHGIN</sub> = 0V, SEAL mode, LDO2<br>disabled                                                                                                                  |      | 0.25 |      |       |  |

|                                                          |                         | V <sub>CHGIN</sub> = 0V, OFF mode, LDO2 enabled,<br>L2IN connected to BAT, Fuel Gauge<br>contribution not included                                                    |      | 1.50 |      |       |  |

|                                                          |                         | V <sub>CHGIN</sub> = 0V, Battery Recovery (BR)<br>mode, LDO2 disabled, Fuel Gauge<br>contribution not included                                                        |      | 1.35 |      |       |  |

| BAT Input Current                                        | IBAT                    | V <sub>CHGIN</sub> = 0V, ON mode, LDO2 disabled,<br>all other rails disabled, Fuel Gauge<br>contribution not included                                                 |      | 1.50 |      | μΑ    |  |

|                                                          | BAI                     | V <sub>CHGIN</sub> = 0V, ON mode, LDO2 disabled,<br>Buck1 enabled, all other rails disabled,<br>Fuel Gauge contribution not included                                  |      | 1.87 |      |       |  |

|                                                          |                         | V <sub>CHGIN</sub> = 0V, ON mode, LDO2 disabled,<br>Buck1 enabled, Buck2 enabled, all other<br>rails disabled, Fuel Gauge contribution<br>not included                |      |      |      |       |  |

|                                                          |                         | V <sub>CHGIN</sub> = 0V, ON mode, LDO2 disabled,<br>Buck1 enabled, Buck2 enabled, Buck3<br>enabled, all other rails disabled, Fuel<br>Gauge contribution not included |      | 2.69 |      |       |  |

| INTERNAL SUPPLIES, U                                     | IVLOS, AND BA           | ГОСР                                                                                                                                                                  |      |      |      |       |  |

| V <sub>CCINT</sub> OTP OK                                | VOONT OTD               | V <sub>CCINT</sub> rising (Note 2)                                                                                                                                    |      | 2.92 | 3.25 |       |  |

| Threshold / Startup<br>Voltage                           | VCCINT_OTP_<br>OK       | V <sub>CCINT</sub> falling (Note 2)                                                                                                                                   | 2.60 | 2.90 |      | V     |  |

| V <sub>DIG</sub> OTP OK                                  | V <sub>DIG_OTP_OK</sub> | V <sub>DIG</sub> rising                                                                                                                                               |      | 1.52 | 1.62 | - v   |  |

| Threshold                                                | *DIG_OTP_OK             | V <sub>DIG</sub> falling                                                                                                                                              | 1.41 | 1.51 |      | · ·   |  |

| V <sub>CCINT</sub> UVLO                                  | V <sub>CCINT_UVLO</sub> | V <sub>CCINT</sub> rising (Note 2)                                                                                                                                    | 2.20 | 2.45 | 2.75 | - v   |  |

| Threshold (POR)                                          |                         | V <sub>CCINT</sub> falling (Note 2)                                                                                                                                   | 2.15 | 2.40 | 2.70 | · ·   |  |

| V <sub>CCINT</sub> UVLO<br>Threshold (POR)<br>Hysteresis | V <sub>CCINT_UVLO</sub> | (Note 2)                                                                                                                                                              |      | 50   |      | mV    |  |

| Internal VDIG Regulator                                  | V <sub>DIG</sub>        |                                                                                                                                                                       | 1.71 | 1.80 | 1.89 | V     |  |

|                                                          | Maria                   | V <sub>DIG</sub> rising                                                                                                                                               | 1.59 |      | 1.73 | N     |  |

| V <sub>DIG</sub> UVLO Threshold V                        | V <sub>DIG_UVLO</sub>   | LO V <sub>DIG</sub> falling                                                                                                                                           |      |      | 1.61 | - V   |  |

| V <sub>DIG</sub> UVLO Threshold<br>Hysteresis            | VDIG_UVLO_H             |                                                                                                                                                                       |      | 100  |      | mV    |  |

| Internal CAP Regulator                                   | V <sub>CAP</sub>        | V <sub>CHGIN</sub> = 4.3V to 28.0V                                                                                                                                    | 3.75 | 4.10 | 4.55 | V     |  |

| CAD Datast Threehold                                     | Mana                    | V <sub>CHGIN</sub> = V <sub>CAP</sub> rising                                                                                                                          | 3.15 | 3.40 | 3.60 |       |  |

| CAP Detect Threshold                                     | V <sub>CAP_DET</sub>    | V <sub>CHGIN</sub> = V <sub>CAP</sub> falling                                                                                                                         | 2.60 | 2.80 | 3.00 | V     |  |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

### **Electrical Characteristics (continued)**

| PARAMETER                                 | SYMBOL                          | CONI                                                                                 | DITIONS                                     | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------|------|------|------|-------|

| CAP Detect Threshold<br>Hysteresis        | V <sub>CAP_DET_H</sub>          |                                                                                      |                                             |      | 600  |      | mV    |

| CHGIN Detect                              | Valiant PET                     | V <sub>CHGIN</sub> rising                                                            |                                             | 4.00 | 4.15 | 4.30 | - V   |

| Threshold                                 | VCHGIN_DET                      | V <sub>CHGIN</sub> falling                                                           |                                             | 3.20 | 3.30 | 3.40 | v     |

| CHGIN Detect<br>Threshold Hysteresis      | V <sub>CHGIN_DET_</sub><br>H    |                                                                                      |                                             |      | 850  |      | mV    |

| CHGIN Detection                           | touonu prz                      | CHGIN insertion                                                                      |                                             |      | 108  |      | ms    |

| Debounce Time                             | <sup>t</sup> CHGIN_DET          | CHGIN detachment                                                                     | t                                           |      | 100  |      | 1115  |

|                                           |                                 |                                                                                      | V <sub>SYS</sub> rising,<br>VSysUvlo = 00   | 2.65 | 2.75 | 2.85 |       |

|                                           |                                 |                                                                                      | V <sub>SYS</sub> falling,<br>VSysUvlo = 00  | 2.60 | 2.70 | 2.80 |       |

| SYS UVLO Threshold                        | V <sub>SYS_UVLO</sub>           | Device Specific<br>(see <u>Table 8</u> )                                             | V <sub>SYS</sub> falling,<br>VSysUvlo = 01  | 2.80 | 2.90 | 3.00 | V     |

|                                           |                                 |                                                                                      | V <sub>SYS</sub> falling,<br>VSysUvlo = 10  | 2.90 | 3.00 | 3.10 |       |

|                                           |                                 |                                                                                      | V <sub>SYS</sub> falling,<br>VSysUvlo = 11  | 3.10 | 3.20 | 3.30 |       |

| SYS UVLO Threshold<br>Hysteresis          | V <sub>SYS_UVLO_H</sub>         |                                                                                      |                                             |      | 50   |      | mV    |

| SYS UVLO Falling<br>Debounce Time         | t <sub>SYS_UVLO_F</sub>         | V <sub>SYS</sub> falling                                                             |                                             |      | 20   |      | μs    |

| BAT OCP Threshold                         | IBAT_OCP_AC                     | I <sub>SYS</sub> rising, thresho<br>400mA in 200mA st<br>(see IBatOc in <u>Tabl</u>  | teps, device specific                       | -50  |      | +50  |       |

| Accuracy                                  | C                               | I <sub>SYS</sub> rising, thresho<br>1.6A in 200mA step<br>IBatOc in <u>Table 8</u> ) | ld from 600mA to<br>s, device specific (see | -40  |      | +40  | - %   |

| BAT OCP Threshold<br>Hysteresis           | IBAT_OCP_H                      |                                                                                      |                                             |      | 7    |      | %     |

| BAT OCP Rising<br>Debounce Time           | <sup>t</sup> BAT_OCP_RD         | I <sub>SYS</sub> rising                                                              |                                             |      | 50   |      | ms    |

| OVP AND INPUT CURR                        | ENT LIMITER                     |                                                                                      | ·                                           |      |      |      |       |

| CHGIN Overvoltage<br>Threshold            | V <sub>CHGIN_OV</sub>           | V <sub>CHGIN</sub> rising                                                            |                                             | 7.2  | 7.5  | 7.8  | V     |

| CHGIN Overvoltage<br>Threshold Hysteresis | V <sub>CHGIN_OV_H</sub>         |                                                                                      |                                             |      | 200  |      | mV    |

| CHGIN-SYS Valid Trip<br>Point             | V <sub>CHGIN_SYS_</sub><br>TP   | V <sub>CHGIN</sub> - V <sub>SYS</sub> risiı                                          | ng                                          | 30   | 145  | 290  | mV    |

| CHGIN-SYS Valid Trip<br>Point Hysteresis  | V <sub>CHGIN_SYS_</sub><br>TP_H |                                                                                      |                                             |      | 275  |      | mV    |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

### **Electrical Characteristics (continued)**

| PARAMETER                         | SYMBOL                         | CON                                       | DITIONS                                      | MIN                                           | TYP                                        | MAX                                           | UNITS |            |

|-----------------------------------|--------------------------------|-------------------------------------------|----------------------------------------------|-----------------------------------------------|--------------------------------------------|-----------------------------------------------|-------|------------|

| Input Overcurrent Max             |                                |                                           | Device Specific                              | t < t <sub>ILIM_BLANK</sub> ,<br>ILimMax = 0  | 400                                        | 450                                           | 500   | <b>m</b> ( |

| Limit                             | LIM_MAX                        | (see <u>Table 8</u> )                     | t < t <sub>ILIM_BLANK</sub> ,<br>ILimMax = 1 | 800                                           | 1000                                       | 1250                                          | mA    |            |

|                                   |                                | ILimCntl = 000                            |                                              |                                               | 50                                         |                                               |       |            |

|                                   |                                | ILimCntl = 001                            |                                              |                                               | 90                                         |                                               |       |            |

|                                   |                                | ILimCntl = 010                            |                                              |                                               | 150                                        |                                               |       |            |

| Innut Current Limit               |                                | ILimCntl = 011                            |                                              |                                               | 200                                        |                                               |       |            |

| Input Current Limit               | ILIM                           | ILimCntl = 100                            |                                              |                                               | 300                                        |                                               | mA    |            |

|                                   |                                | ILimCntl = 101                            |                                              |                                               | 400                                        |                                               |       |            |

|                                   |                                | ILimCntl = 110                            |                                              | 400                                           | 450                                        | 500                                           |       |            |

|                                   |                                | ILimCntl = 111                            |                                              | 900                                           | 1000                                       | 1100                                          |       |            |

|                                   |                                | ILimBlank = 00                            |                                              |                                               | 0.0                                        |                                               |       |            |

| Input Current-Limit               |                                | ILimBlank = 01                            |                                              |                                               | 0.5                                        |                                               |       |            |

| Blanking Time                     | <sup>t</sup> ILIM_BLANK        | ILimBlank = 10                            |                                              |                                               | 1.0                                        |                                               | ms    |            |

|                                   |                                | ILimBlank = 11                            |                                              |                                               | 10.0                                       |                                               | 1     |            |

| SYS Regulation Voltage            | V <sub>SYS_REG</sub>           |                                           |                                              | V <sub>BAT_R</sub><br>EG <sup>+</sup><br>0.14 | V <sub>BAT_RE</sub><br><sub>G</sub> + 0.20 | V <sub>BAT_R</sub><br>EG <sup>+</sup><br>0.26 | V     |            |

| SYS Regulation-Voltage<br>Dropout | V <sub>CHGIN</sub> SYS_<br>REG |                                           |                                              |                                               | 40                                         |                                               | mV    |            |

| CHGIN to SYS On<br>Resistance     | R <sub>CHGIN_SYS</sub>         |                                           |                                              |                                               | 0.37                                       | 0.66                                          | Ω     |            |

| Input Current Soft-Start<br>Time  | tILIM_SFT                      |                                           |                                              |                                               | 1                                          |                                               | ms    |            |

|                                   |                                |                                           | TShdn = 000                                  |                                               | 50                                         |                                               |       |            |

|                                   |                                |                                           | TShdn = 001                                  |                                               | 60                                         |                                               |       |            |

|                                   |                                |                                           | TShdn = 010                                  |                                               | 70                                         |                                               |       |            |

| Thermal Shutdown                  | -<br>-                         | Device Specific                           | TShdn = 011                                  |                                               | 80                                         |                                               | *0    |            |

| Temperature                       | TCHG_SHDN                      | (see Table 8)                             | TShdn = 100                                  |                                               | 90                                         |                                               | °C    |            |

|                                   |                                |                                           | TShdn = 101                                  |                                               | 100                                        |                                               |       |            |

|                                   |                                | TShdn = 110                               |                                              |                                               | 110                                        |                                               | 1     |            |

|                                   |                                |                                           | TShdn = 111                                  |                                               | 120                                        |                                               |       |            |

| CHGIN Boot Retry<br>Timeout       | t <sub>CHG_RETRY_</sub><br>TMO | ChgAlwTry = 1, De<br><u>Table 8</u> )     | vice Specific (see                           |                                               | 0.5                                        |                                               | S     |            |

| BATTERY CHARGER                   |                                |                                           |                                              |                                               |                                            |                                               |       |            |

| BAT to SYS On<br>Resistance       | R <sub>BAT_SYS</sub>           | V <sub>BAT</sub> = 4.2V, I <sub>BAT</sub> | = 300mA                                      |                                               | 80                                         | 140                                           | mΩ    |            |

## PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

### **Electrical Characteristics (continued)**

$(V_{BAT} = V_{FGBAT} = V_{SYS\_UVLO} (falling) to +5.5V, V_{CHGIN} = unconnected or V_{CHGIN\_DET} to +28.0V, T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C, V_{BAT} = 3.7V, V_{CHGIN} = 5.0V, C_{CHGIN\_EFF} = 1\muF, C_{VDIG\_EFF} = 1\muF, C_{CAP\_EFF} = 1\muF, C_{SYS\_EFF} = 10\muF, C_{BAT\_EFF} = 1\muF, C_{BK\_OUT\_EFF} = 10\muF, C_{L\_IN} = 1\muF, C_{L\_OUT\_EFF} = 1\muF, C_{BBOUT\_EFF} = 8.8\muF, C_{BSTOUT\_EFF} = 10\muF, L_{BK\_OUT} = 2.2\muH, L_{BBOUT} = 2.2\muH, L_{BSTOUT\_EFT} = 4.7\muH. Limits are 100\% tested at T_A = +25^{\circ}C.) (Note 1)$

| PARAMETER                                           | SYMBOL                       | CO                                                          | NDITIONS                                            | MIN                         | TYP                                      | MAX                         | UNITS |  |

|-----------------------------------------------------|------------------------------|-------------------------------------------------------------|-----------------------------------------------------|-----------------------------|------------------------------------------|-----------------------------|-------|--|

| Thermal Regulation<br>Temperature                   | T <sub>CHG_LIM</sub>         |                                                             |                                                     |                             | T <sub>CHG_S</sub><br><sub>HDN</sub> - 3 |                             | °C    |  |

| BAT to SYS Switch On<br>Threshold                   | VBAT_SYS_ON                  | $V_{SYS}$ falling, mea                                      | asured as $V_{BAT}$ - $V_{SYS}$                     | 10                          | 19                                       | 35                          | mV    |  |

| BAT to SYS Switch Off<br>Threshold                  | V <sub>BAT_SYS_OF</sub>      | V <sub>SYS</sub> rising, mea                                | sured as $V_{BAT}$ - $V_{SYS}$                      | -3                          | -1                                       | 0                           | mV    |  |

| SYS to BAT Charge<br>Current Reduction<br>Threshold | V <sub>SYS_BAT_RE</sub><br>G | Measured as V <sub>SV</sub><br>000, V <sub>BAT</sub> > 3.6V | <sub>YS</sub> - V <sub>BAT</sub> , SysMinVIt =<br>/ |                             | 100                                      |                             | mV    |  |

|                                                     |                              |                                                             | SysMinVIt = 000                                     |                             | 3.6                                      |                             |       |  |

|                                                     |                              |                                                             | SysMinVIt = 001                                     |                             | 3.7                                      |                             |       |  |

|                                                     |                              |                                                             | SysMinVIt = 010                                     |                             | 3.8                                      |                             |       |  |

| Minimum CVC Valtage                                 |                              | V 2 AV                                                      | SysMinVIt = 011                                     |                             | 3.9                                      |                             |       |  |

| Minimum SYS Voltage                                 | V <sub>SYS_LIM</sub>         | V <sub>BAT</sub> < 3.4V                                     | SysMinVIt = 100                                     |                             | 4.0                                      |                             | V     |  |

|                                                     |                              |                                                             | SysMinVIt = 101                                     |                             | 4.1                                      |                             | -     |  |

|                                                     |                              |                                                             | SysMinVIt = 110                                     |                             | 4.2                                      |                             |       |  |

|                                                     |                              |                                                             | SysMinVIt = 111                                     |                             | 4.3                                      |                             |       |  |

| Charger Current Soft-<br>Start Time                 | <sup>t</sup> ICHG_SFT        |                                                             |                                                     |                             | 1                                        |                             | ms    |  |

|                                                     |                              | IPChg = 00                                                  |                                                     |                             | 0.05 x<br>I <sub>FCHG</sub>              |                             |       |  |

| Precharge Current                                   |                              | IPChg = 01                                                  |                                                     | 0.09 x<br>I <sub>FCHG</sub> | 0.10 x<br>I <sub>FCHG</sub>              | 0.11 x<br>I <sub>FCHG</sub> |       |  |

|                                                     | IPCHG                        | IPChg = 10                                                  |                                                     |                             | 0.20 x<br>I <sub>FCHG</sub>              |                             | - mA  |  |

|                                                     |                              | IPChg = 11                                                  | PChg = 11                                           |                             | 0.30 x<br>I <sub>FCHG</sub>              |                             |       |  |

|                                                     |                              |                                                             | VPChg = 000                                         |                             | 2.10                                     |                             |       |  |

|                                                     |                              |                                                             | VPChg = 001                                         |                             | 2.25                                     |                             |       |  |

|                                                     |                              |                                                             | VPChg = 010                                         |                             | 2.40                                     |                             |       |  |

| Drochargo Throchold                                 |                              |                                                             | VPChg = 011                                         |                             | 2.55                                     |                             | v     |  |

| Precharge Threshold                                 | V <sub>BAT_PCHG</sub>        | V <sub>BAT</sub> rising                                     | VPChg = 100                                         |                             | 2.70                                     |                             | v     |  |

|                                                     |                              |                                                             | VPChg = 101                                         |                             | 2.85                                     |                             | _     |  |

|                                                     |                              |                                                             | VPChg = 110                                         |                             | 3.00                                     |                             |       |  |

|                                                     |                              |                                                             | VPChg = 111                                         |                             | 3.15                                     |                             |       |  |

| Precharge Threshold<br>Hysteresis                   | V <sub>BAT_PCHG_H</sub>      |                                                             |                                                     |                             | 90                                       |                             | mV    |  |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

### **Electrical Characteristics (continued)**

| PARAMETER             | SYMBOL      | COND                    | ITIONS                | MIN | TYP  | MAX | UNITS |

|-----------------------|-------------|-------------------------|-----------------------|-----|------|-----|-------|

|                       |             |                         | ChgStepRise =<br>0000 |     | 3.80 |     |       |

|                       |             |                         | ChgStepRise =<br>0001 |     | 3.85 |     |       |

|                       |             |                         | ChgStepRise =<br>0010 |     | 3.90 |     |       |

|                       |             |                         | ChgStepRise =<br>0011 |     | 3.95 |     |       |

| Step-Charge Threshold |             |                         | ChgStepRise =<br>0100 |     | 4.00 |     |       |

|                       |             |                         | ChgStepRise =<br>0101 |     | 4.05 |     |       |

|                       |             |                         | ChgStepRise =<br>0110 |     | 4.10 |     |       |

|                       | VBAT_STPCHG | V <sub>BAT</sub> rising | ChgStepRise =<br>0111 |     | 4.15 |     |       |

|                       |             |                         | ChgStepRise =<br>1000 |     | 4.20 |     |       |

|                       |             |                         | ChgStepRise =<br>1001 |     | 4.25 |     |       |

|                       |             |                         | ChgStepRise =<br>1010 |     | 4.30 |     |       |

|                       |             |                         | ChgStepRise =<br>1011 |     | 4.35 |     |       |

|                       |             |                         | ChgStepRise =<br>1100 |     | 4.40 |     |       |

|                       |             |                         | ChgStepRise =<br>1101 |     | 4.45 |     |       |

|                       |             |                         | ChgStepRise =<br>1110 |     | 4.50 |     |       |

|                       |             |                         | ChgStepRise =<br>1111 |     | 4.55 |     |       |

|                       |             | ChgStepHys = 000        |                       |     | 100  |     |       |

|                       |             | ChgStepHys = 001        |                       |     | 200  |     |       |

| Step-Charge Threshold | VBAT_STPCHG | ChgStepHys = 010        |                       |     | 300  |     | mV    |

| Hysteresis            | _H          | ChgStepHys = 011        |                       |     | 400  |     |       |

|                       |             | ChgStepHys = 100        |                       |     | 500  |     |       |

|                       |             | ChgStepHys = 101        |                       |     | 600  |     | ]     |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

#### **Electrical Characteristics (continued)**

$(V_{BAT} = V_{FGBAT} = V_{SYS\_UVLO} (falling) to +5.5V, V_{CHGIN} = unconnected or V_{CHGIN\_DET} to +28.0V, T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C, V_{BAT} = 3.7V, V_{CHGIN} = 5.0V, C_{CHGIN\_EFF} = 1\muF, C_{VDIG\_EFF} = 1\muF, C_{CAP\_EFF} = 1\muF, C_{SYS\_EFF} = 10\muF, C_{BAT\_EFF} = 1\muF, C_{BK\_OUT\_EFF} = 10\muF, C_{L\_IN} = 1\muF, C_{L\_OUT\_EFF} = 1\muF, C_{BBOUT\_EFF} = 8.8\muF, C_{BSTOUT\_EFF} = 10\muF, L_{BK\_OUT} = 2.2\muH, L_{BBOUT} = 2.2\muH, L_{BSTOUT} = 4.7\muH. Limits are 100\% tested at T_A = +25^{\circ}C.) (Note 1)$

| PARAMETER                                              | SYMBOL            | CONDITIONS                | MIN | TYP                        | MAX | UNITS |  |  |

|--------------------------------------------------------|-------------------|---------------------------|-----|----------------------------|-----|-------|--|--|

|                                                        |                   | ChglStep = 000            |     | 0.2 x<br>I <sub>FCHG</sub> |     |       |  |  |

| Fast-Charge Current<br>Reduction Due to Step<br>Charge |                   | ChglStep = 001            |     | 0.3 x<br>I <sub>FCHG</sub> |     |       |  |  |

|                                                        |                   | ChglStep = 010            |     | 0.4 x<br>I <sub>FCHG</sub> |     |       |  |  |

|                                                        | IFCHG_STPCH       | ChglStep = 011            |     | 0.5 x<br>I <sub>FCHG</sub> |     | mA    |  |  |

|                                                        | G                 | ChglStep = 100            |     | 0.6 x<br>I <sub>FCHG</sub> |     |       |  |  |

|                                                        |                   | ChglStep = 101            |     | 0.7 x<br>I <sub>FCHG</sub> |     |       |  |  |

|                                                        |                   | ChglStep = 110            |     | 0.8 x<br>I <sub>FCHG</sub> |     |       |  |  |

|                                                        |                   | ChglStep = 111            |     | I <sub>FCHG</sub>          |     |       |  |  |

| ISET Current Gain<br>Factor                            | K <sub>ISET</sub> |                           |     | 2000                       |     | A/A   |  |  |

| ISET Regulation Voltage                                | VISET             |                           |     | 1                          |     | V     |  |  |

|                                                        |                   | R <sub>ISET</sub> = 400kΩ |     | 5                          |     |       |  |  |

| BAT Fast-Charge<br>Current Set Range                   | IFCHG             | R <sub>ISET</sub> = 40kΩ  | 45  | 50                         | 55  | mA    |  |  |

|                                                        |                   | R <sub>ISET</sub> = 4kΩ   |     | 500                        |     | 7     |  |  |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

#### **Electrical Characteristics (continued)**

| PARAMETER           | SYMBOL               | COND             | ITIONS                                | MIN              | TYP    | MAX    | UNITS |

|---------------------|----------------------|------------------|---------------------------------------|------------------|--------|--------|-------|

|                     |                      | ChgBatReg = 0000 |                                       |                  | 4.0500 |        |       |

|                     |                      | ChgBatReg = 0001 |                                       |                  | 4.1000 |        |       |

|                     |                      | ChgBatReg = 0010 |                                       |                  | 4.1500 |        |       |

|                     |                      |                  | T <sub>A</sub> = 25°C                 | 4.1853           | 4.2000 | 4.2147 |       |

|                     |                      | ChgBatReg = 0011 | $T_A = -5^{\circ}C$ to $+50^{\circ}C$ | 4.1769           | 4.2000 | 4.2231 |       |

|                     |                      |                  |                                       | 4.1622           | 4.2000 | 4.2378 |       |

|                     |                      | ChgBatReg = 0100 |                                       |                  | 4.2500 |        |       |

|                     |                      | ChgBatReg = 0101 |                                       |                  | 4.3000 |        |       |

| Battery-Regulation  |                      | ChgBatReg = 0110 |                                       |                  | 4.3500 |        | V     |

| Voltage             | V <sub>BAT_REG</sub> |                  | T <sub>A</sub> = 25°C                 | 4.3846           | 4.4000 | 4.4154 |       |

|                     |                      |                  | $T_A = -5^{\circ}C$ to $+50^{\circ}C$ | 4.3758           | 4.4000 | 4.4242 |       |

|                     |                      |                  |                                       | 4.3604           | 4.4000 | 4.4396 |       |

|                     |                      | ChgBatReg = 1000 | T <sub>A</sub> = 25°C                 | 4.4344           | 4.4500 | 4.4656 |       |

|                     |                      |                  | $T_A = -5^{\circ}C$ to $+50^{\circ}C$ | 4.4255           | 4.4500 | 4.4745 |       |

|                     |                      |                  |                                       | 4.4099           | 4.4500 | 4.4901 |       |

|                     |                      | ChgBatReg = 1001 |                                       |                  | 4.5000 |        |       |

|                     |                      | ChgBatReg = 1010 |                                       | 4.5500<br>4.6000 |        |        |       |

|                     |                      | ChgBatReg = 1011 |                                       |                  |        |        |       |

|                     |                      | ChgBatReChg = 00 |                                       | 70               |        |        |       |

| Battery-Recharge    |                      | ChgBatReChg = 01 |                                       |                  | 120    |        | mV    |

| Threshold           | VBAT_RECHG           | ChgBatReChg = 10 |                                       |                  | 170    |        | mv    |

|                     |                      | ChgBatReChg = 11 |                                       |                  | 220    |        |       |

|                     |                      | PChgTmr = 00     |                                       |                  | 30     |        |       |

| Maximum Precharge   |                      | PChgTmr = 01     |                                       |                  | 60     |        |       |

| Time                | <sup>t</sup> PCHG    | PChgTmr = 10     |                                       |                  | 120    |        | min   |

|                     |                      | PChgTmr = 11     |                                       |                  | 240    |        |       |

|                     |                      | FChgTmr = 00     |                                       |                  | 75     |        |       |

| Maximum Fast-Charge | <b>t</b>             | FChgTmr = 01     |                                       | 150              |        |        |       |

| Time                | tFCHG -              | FChgTmr = 10     |                                       | 300              |        |        | — min |

|                     |                      | FChgTmr = 11     |                                       |                  | 600    |        | 1     |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

#### **Electrical Characteristics (continued)**

| PARAMETER                                                     | SYMBOL                  | CONDITIONS                   | MIN                          | TYP                                        | MAX                          | UNITS              |  |  |

|---------------------------------------------------------------|-------------------------|------------------------------|------------------------------|--------------------------------------------|------------------------------|--------------------|--|--|

|                                                               |                         | IChgDone = 00                |                              | 0.050 x<br>I <sub>FCHG</sub>               |                              |                    |  |  |

| Charge Done                                                   |                         | IChgDone = 01                | 0.085 x<br>I <sub>FCHG</sub> | 0.100 x<br>I <sub>FCHG</sub>               | 0.115 x<br>I <sub>FCHG</sub> |                    |  |  |

| Qualification                                                 | ICHG_DONE               | IChgDone = 10                |                              | 0.200 x<br>I <sub>FCHG</sub>               |                              | mA                 |  |  |

|                                                               |                         | IChgDone = 11                |                              | 0.300 x<br><sup>I</sup> FCHG               |                              |                    |  |  |

|                                                               |                         | MtChgTmr = 00                |                              | 0                                          |                              |                    |  |  |

| Maximum Maintain                                              | <b>4</b>                | MtChgTmr = 01                |                              | 15                                         |                              |                    |  |  |

| Charge Time                                                   | <sup>t</sup> мтснg      | MtChgTmr = 10                |                              | 30                                         |                              |                    |  |  |

|                                                               |                         | MtChgTmr = 11                |                              | 60                                         |                              |                    |  |  |

| Timer Accuracy                                                | t <sub>CHG_ACC</sub>    |                              | -10                          |                                            | +10                          | %                  |  |  |

| Fast-Charge Timer<br>Extend Current<br>Threshold              | IFCHG_TEXT              | See Figure 32                |                              | 50                                         |                              | %I <sub>FCHG</sub> |  |  |

| Fast-Charge Timer<br>Suspend Current<br>Threshold             | IFCHG_TSUS              | See Figure 32                |                              | 20                                         |                              | %I <sub>FCHG</sub> |  |  |

|                                                               |                         | ChgCool/Room/WarmBatReg = 00 |                              | V <sub>BAT_RE</sub><br><sub>G</sub> - 0.15 |                              |                    |  |  |

| Battery Regulation<br>Voltage Reduction Due<br>to Temperature | V <sub>BAT_REG_JT</sub> | ChgCool/Room/WarmBatReg = 01 |                              | V <sub>BAT_RE</sub><br>G - 0.1             |                              |                    |  |  |

|                                                               | A                       | ChgCool/Room/WarmBatReg = 10 |                              | V <sub>BAT_RE</sub><br><sub>G</sub> - 0.05 |                              |                    |  |  |

|                                                               |                         | ChgCool/Room/WarmBatReg = 11 |                              | V <sub>BAT_RE</sub><br>G                   |                              |                    |  |  |

# PMIC with Ultra-Low I<sub>Q</sub> Regulators, Charger, Fuel Gauge, and Haptic Driver for Small Li+ System

#### **Electrical Characteristics (continued)**

$(V_{BAT} = V_{FGBAT} = V_{SYS\_UVLO} (falling) to +5.5V, V_{CHGIN} = unconnected or V_{CHGIN\_DET} to +28.0V, T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C, V_{BAT} = 3.7V, V_{CHGIN} = 5.0V, C_{CHGIN\_EFF} = 1\muF, C_{VDIG\_EFF} = 1\muF, C_{CAP\_EFF} = 1\muF, C_{SYS\_EFF} = 10\muF, C_{BAT\_EFF} = 1\muF, C_{BK\_OUT\_EFF} = 10\muF, C_{L\_IN} = 1\muF, C_{L\_OUT\_EFF} = 1\muF, C_{BBOUT\_EFF} = 8.8\muF, C_{BSTOUT\_EFF} = 10\muF, L_{BK\_OUT} = 2.2\muH, L_{BBOUT} = 2.2\muH, L_{BSTOUT} = 4.7\muH. Limits are 100\% tested at T_A = +25^{\circ}C.) (Note 1)$

| PARAMETER                                                            | SYMBOL                                        | CONDITIONS                                                                                                                                                           | MIN  | TYP                         | MAX  | UNITS |

|----------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------|------|-------|

|                                                                      |                                               | ChgCool/Room/WarmIFChg = 000                                                                                                                                         |      | 0.20 x<br>I <sub>FCHG</sub> |      |       |

|                                                                      |                                               | ChgCool/Room/WarmIFChg = 001                                                                                                                                         |      | 0.30 x<br>I <sub>FCHG</sub> |      |       |

|                                                                      |                                               | ChgCool/Room/WarmIFChg = 010 0.40 x<br>IFCHG                                                                                                                         |      |                             |      |       |

| Fast-Charge Current<br>Reduction Due to                              | IFCHG_JTA                                     | ChgCool/Room/WarmIFChg = 011                                                                                                                                         |      | 0.50 x<br>I <sub>FCHG</sub> |      | mA    |

| Temperature                                                          |                                               | ChgCool/Room/WarmIFChg = 100                                                                                                                                         |      | 0.60 x<br>I <sub>FCHG</sub> |      |       |

|                                                                      |                                               | ChgCool/Room/WarmIFChg = 101                                                                                                                                         |      | 0.70 x<br>I <sub>FCHG</sub> |      |       |

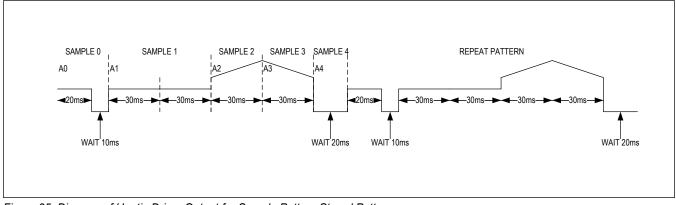

|                                                                      |                                               | ChgCool/Room/WarmIFChg = 110                                                                                                                                         |      | 0.80 x<br>I <sub>FCHG</sub> |      |       |