### MAX20094/MAX20095

# **Backup Battery Charger and Boost Controller**

### **General Description**

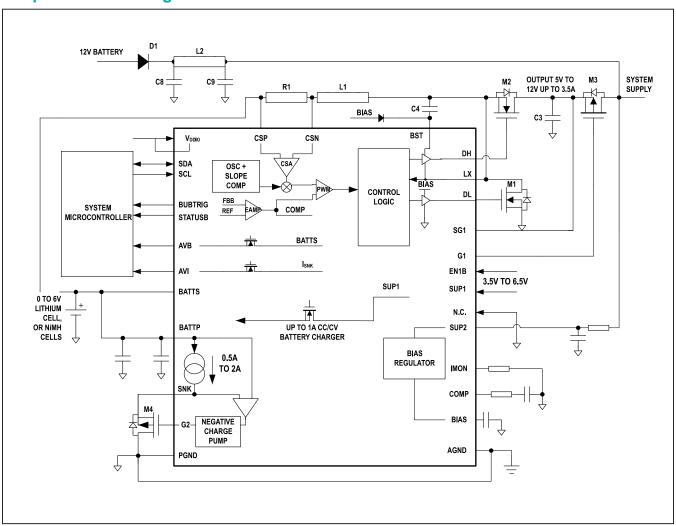

The MAX20094/MAX20095 ICs combine a configurable constant-current/constant-voltage (CC/CV) battery charger with a high-efficiency synchronous boost controller to supply critical systems in the event the primary power source is lost. In addition, diagnostic features are available to check battery state-of-health (SOH) and IC functionality. Charging thresholds and the boost output voltage are configurable to support popular battery chemistries and a wide range of cell counts. To support system integration, the ICs have an I<sup>2</sup>C slave port through which configuration and status bits can be accessed.

Switching frequency of 2.2MHz also helps to reduce system cost by minimizing inductor size. The ICs also include a precision battery SOH check and have built-in functionality to minimize leakage current out of the back-up battery (BUB).

The MAX20094/MAX20095 are available in a 28-pin (5mm x 5mm) side-wettable TQFN package and are AECQ-100 qualified.

# **Applications**

- Automotive Telematics Battery Backup

- Single or Multicell Battery-Backup Systems

#### **Benefits and Features**

- Efficient Solution

- Minimum 2V Sync Boost with n-Channel FET Control

- Skip Mode Guarantees > 50% Efficiency at 1mA

- Multiple Functions to Enable Small Solution Size

- · 3V to 6V CC/CV Battery Charger

- I<sup>2</sup>C-Settable Charging Current Up to 1A

- I<sup>2</sup>C-Selectable CV Voltage and CC Current Levels

- · Gate-Driver Output for p-Channel Load Disconnect

- · Backup Battery Switchover-Trigger Signal

- State-of-Health for Backup Battery Monitoring

- I<sup>2</sup>C Interface Diagnostics and Control Interface

- Accurate Internal Current Sink for Battery Impedance Measurement

- Analog Readout of Internal Sink Current from Backup Battery

- Remote Sense for BATT\_ Voltage Measurement

- Robust for Automotive Environment

- 3.5V to 36V V<sub>IN</sub> (40V Load-Dump Tolerant)

- < 1µA Leakage for Pins Connected to the Battery</li>

- -40°C to +125°C Operating Temperature Range

- 28-Pin, Side-Wettable TQFN Package Enables Optical Inspection

Ordering Information appears at end of data sheet.

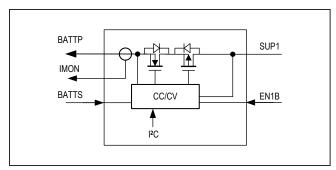

# **Simplified Block Diagram**

# Backup Battery Charger and Boost Controller

# **Absolute Maximum Ratings**

| SUP2, DH, LX, SG1, CSP, CSN to PGND0.3V to +40V  | BATTP, SNK, BATTS, SUP1 to AGND0.3V to +7.0V |

|--------------------------------------------------|----------------------------------------------|

| G1 to SG17.0V to +0.3V                           | AVB to AGND0.3V to V <sub>BATTS</sub> + 0.3V |

| BST to LX0.3V to +6V                             | G2 to BATTP6.0V to +0.3V                     |

| CSP to CSN0.3V to +0.3V                          | Operating Temperature Range40°C to +125°C    |

| AVI, BUBTRIG, DL, COMP,                          | Junction Temperature+150°C                   |

| IMON to AGND0.3V to V <sub>BIAS</sub> + 0.3V     | Storage Temperature Range40°C to +150°C      |

| SCL, SDA to AGND0.3V to V <sub>DDIO</sub> + 0.3V | Soldering Temperature (reflow)+260°C         |

| PGND to AGND0.3V to +0.3V                        | ESD Protection - Human Body Model±2kV        |

| EN1B, BIAS, VDDIO, STATUSB to AGND0.3V to +6V    |                                              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 28-Pin (5mm x 5mm x 0.75mm) Side-Wettable TQFN

| PACKAGE CODE                            | T2855Y+5C |

|-----------------------------------------|-----------|

| Outline Number                          | 21-100130 |

| Land Pattern Number                     | 90-0027   |

| Thermal Resistance, Single-Layer Board: |           |

| Junction to Ambient (θ <sub>JA</sub> )  | 48°C/W    |

| Junction to Case (θ <sub>JC</sub> )     | 3°C/W     |

| Thermal Resistance, Four-Layer Board:   |           |

| Junction to Ambient (θ <sub>JA</sub> )  | 35°C/W    |

| Junction to Case (θ <sub>JC</sub> )     | 3°C/W     |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

# **Electrical Characteristics**

$(V_{SUP1}=4V,V_{SUP2}=14V,V_{BATTP}=V_{BATTS}=3.5V,T_{A}=T_{J}=-40^{\circ}C\ to+125^{\circ}C, unless otherwise noted.\ Typical values are at\ T_{A}=+25^{\circ}C.)$  (Note 1)

| PARAMETER                                                                                          | SYMBOL                | CONDITIONS                                                                                                                                                     | MIN   | TYP  | MAX   | UNITS |

|----------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| BOOST CONTROLLER                                                                                   |                       |                                                                                                                                                                |       |      |       | •     |

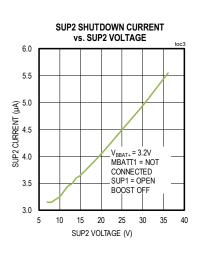

| Supply Voltage Range                                                                               | V <sub>SUP2</sub>     | Normal operation                                                                                                                                               | 4.5   |      | 36    | V     |

| Supply Voltage Range                                                                               |                       | V <sub>SUP2</sub> t < 1s                                                                                                                                       |       |      | 40    | V     |

| Undervoltage-Lockout<br>Threshold                                                                  | V <sub>CSP</sub>      | Contact factory for options                                                                                                                                    |       |      | 2     | V     |

| Shutdown Supply Current                                                                            | I <sub>SUP2</sub>     | Boost disabled through I <sup>2</sup> C, V <sub>SUP2</sub> = 12V, V <sub>EN1B</sub> = 0V                                                                       |       |      | 10    | μA    |

| Supply Current                                                                                     | I <sub>SUP2_STB</sub> | BOOST I <sup>2</sup> C bit enabled, V <sub>EN1B</sub> = 0V, V <sub>SUP1</sub> = 0 to 6V, V <sub>SUP2</sub> = V <sub>SG1</sub> = 14V, no switching              | =     | 26   | 55    | μA    |

|                                                                                                    |                       | MAX20094ATIA                                                                                                                                                   | 6.076 | 6.2  | 6.355 |       |

|                                                                                                    |                       | MAX20094ATIB                                                                                                                                                   | 6.37  | 6.5  | 6.663 |       |

|                                                                                                    |                       | MAX20094ATIC                                                                                                                                                   | 6.664 | 6.8  | 6.97  | 1     |

|                                                                                                    |                       | MAX20094ATID                                                                                                                                                   | 6.958 | 7.1  | 7.278 |       |

| Boost Mode Fixed-Output<br>Voltage                                                                 | V <sub>SUP2</sub>     | MAX20095ATIA                                                                                                                                                   | 5.39  | 5.5  | 5.7   | V     |

| voltage                                                                                            |                       | MAX20095ATIB                                                                                                                                                   | 7.84  | 8    | 8.20  |       |

|                                                                                                    |                       | MAX20095ATIC                                                                                                                                                   | 8.82  | 9    | 9.27  | -     |

|                                                                                                    |                       | MAX20095ATID                                                                                                                                                   | 9.8   | 10   | 10.25 |       |

|                                                                                                    |                       | MAX20095ATIE                                                                                                                                                   | 11.76 | 12   | 12.30 |       |

| Boost Output Overvoltage-<br>Falling Threshold (Boost<br>Wakes Up Below this<br>Threshold)         | BOOST_OV_F            |                                                                                                                                                                | 104   | 107  | 110.5 | %     |

| Boost Output Overvoltage-<br>Falling Hysteresis                                                    |                       |                                                                                                                                                                |       | 6    |       | %     |

| Boost Output Overvoltage-<br>Rising Threshold (Boost<br>Enters Sleep Mode Above<br>this Threshold) | V <sub>SUP2_R</sub>   |                                                                                                                                                                | 110   | 113  | 116   | %     |

| D (11) 1 1 1 1                                                                                     | DOT IN # O            | Falling                                                                                                                                                        |       | 65   |       | 0/    |

| Boost Undervoltage Lockout                                                                         | BST_UVLO              | Rising                                                                                                                                                         |       | 85   |       | %     |

| Transconductance<br>(from FBB to COMP)                                                             | 9 <sub>m</sub>        | V <sub>BIAS</sub> = 5.5V (Note 2)                                                                                                                              |       | 250  |       | μS    |

| G1 Drive Strength                                                                                  | G1                    | V <sub>SG1</sub> = 6.8V, G1 not active                                                                                                                         |       | 1.75 |       | kΩ    |

| G1 Activation Time                                                                                 |                       | 5nF MOSFET capacitance from SG1 to G1,<br>OV falling until G1 reaches 4.5V below SG1;<br>boost is ready to run within 10µs (typ) once<br>BOOST_OV_F is tripped |       | 10   | 50    | μs    |

| D1 T                                                                                               |                       | DL low to DH rising                                                                                                                                            |       | 20   |       |       |

| Dead Time                                                                                          |                       | DH low to DL rising                                                                                                                                            |       | 20   |       | ns    |

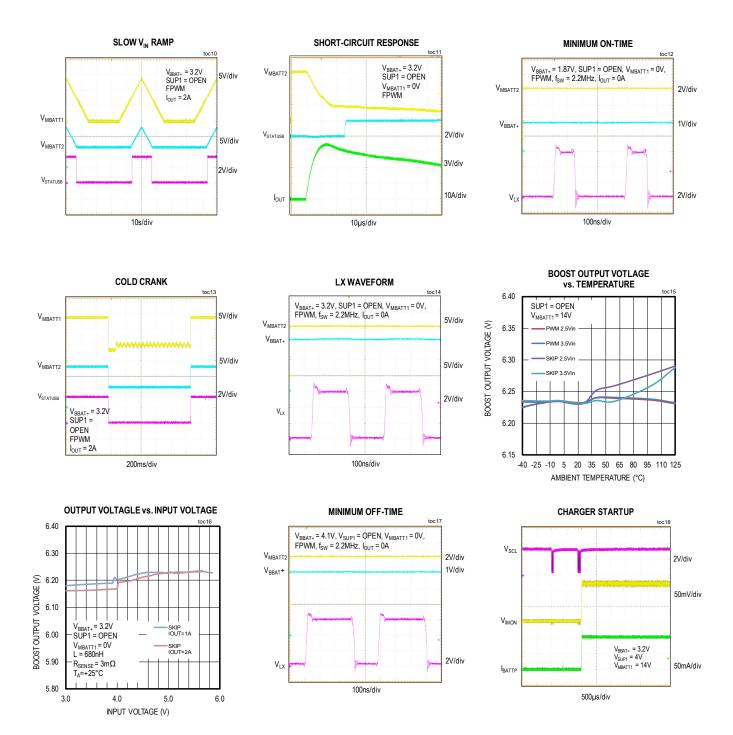

| Minimum On-Time                                                                                    | t <sub>ON,MIN</sub>   |                                                                                                                                                                |       | 120  |       | ns    |

| Minimum Off-Time                                                                                   | t <sub>OFF,MIN</sub>  |                                                                                                                                                                |       | 60   |       | ns    |

# **Electrical Characteristics (continued)**

$(V_{SUP1} = 4V, V_{SUP2} = 14V, V_{BATTP} = V_{BATTS} = 3.5V, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                       | SYMBOL                 | CONDITIONS                                                                                                                                                                                      | MIN  | TYP  | MAX  | UNITS  |

|-------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|

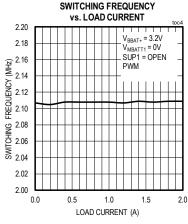

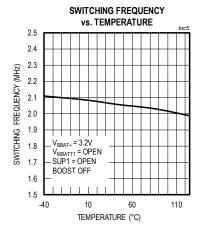

| PWM Switching-Frequency                         | £                      |                                                                                                                                                                                                 | 1.9  | 2.1  | 2.3  | N41.1- |

| Range                                           | f <sub>SW</sub>        | Contact factory for part number                                                                                                                                                                 |      | 0.42 |      | MHz    |

| CS_ Current Limit                               | V <sub>LIMIT</sub>     | V <sub>CSP</sub> - V <sub>CSN</sub>                                                                                                                                                             | 40   | 50   | 60   | mV     |

| LX Leakage Current                              |                        | V <sub>LX</sub> = V <sub>PGND</sub> or V <sub>IN</sub> , T <sub>A</sub> = +25°C                                                                                                                 |      |      | 1    | μA     |

| DH Pullup Resistance                            |                        | V <sub>BIAS</sub> = 5V, I <sub>DH</sub> = -100mA                                                                                                                                                |      | 3    | 6    | Ω      |

| DH Pulldown Resistance                          |                        | V <sub>BIAS</sub> = 5V, I <sub>DH</sub> = 100mA                                                                                                                                                 |      | 1.5  | 3    | Ω      |

| DL Pullup Resistance                            |                        | V <sub>BIAS</sub> = 5V, I <sub>DL</sub> = -100mA                                                                                                                                                |      | 3    | 6    | Ω      |

| DL Pulldown Resistance                          |                        | V <sub>BIAS</sub> = 5V, I <sub>DL</sub> = 100mA                                                                                                                                                 |      | 1.5  | 3    | Ω      |

| INTERNAL LDO BIAS                               |                        |                                                                                                                                                                                                 |      |      |      |        |

| Internal BIAS Voltage                           |                        | V <sub>SUP2</sub> > 6V                                                                                                                                                                          |      | 5    |      | V      |

| DIACUNIC TI.                                    |                        | V <sub>BIAS</sub> rising                                                                                                                                                                        |      | 3.0  | 3.25 | .,     |

| BIAS UVLO Threshold                             |                        | V <sub>BIAS</sub> falling                                                                                                                                                                       | 2.35 | 2.5  |      | V      |

| BATTERY CHARGER                                 |                        |                                                                                                                                                                                                 |      |      |      |        |

| Supply Voltage Range                            | V <sub>SUP1</sub>      |                                                                                                                                                                                                 | 0    |      | 6.5  | V      |

| Supply Undervoltage<br>Threshold, Falling       | V <sub>SUP1_UV</sub>   |                                                                                                                                                                                                 | 3.3  |      |      | V      |

| Supply Undervoltage<br>Threshold, Rising        | V <sub>SUP1_UV_R</sub> |                                                                                                                                                                                                 |      |      | 3.5  | V      |

| Supply Leakage Current                          | I <sub>SUP1</sub>      | Charger disabled, T <sub>A</sub> = +25°C                                                                                                                                                        |      |      | 10   | μA     |

| SUP1 to BATTP<br>On-Resistance                  | R <sub>CHG</sub>       | V <sub>SUP1</sub> = 3.5V, V <sub>BATTP</sub> = 3.45V                                                                                                                                            |      | 250  | 500  | mΩ     |

| I <sup>2</sup> C Control BUB Voltage<br>Setting | V <sub>CVTHR</sub>     | I <sup>2</sup> C control                                                                                                                                                                        | 3.0  |      | 6.0  | V      |

| BUB Voltage Range                               | V <sub>BATT</sub>      |                                                                                                                                                                                                 | 0.0  |      | 6.0  | V      |

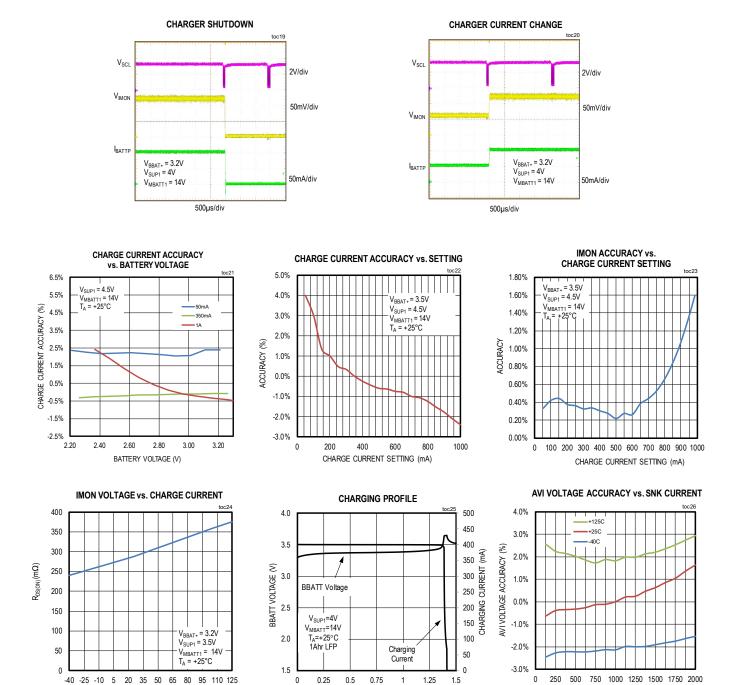

| Output-Voltage Accuracy                         | V <sub>BATT</sub>      | V <sub>CVTHR</sub> = 3.6V                                                                                                                                                                       | -1.2 |      | +1   | %      |

| Fast-Charging Current<br>Setting                | _                      | I <sup>2</sup> C settable                                                                                                                                                                       | 0.05 |      | 1    | Α      |

| Precharge Current                               |                        | V <sub>BUB</sub> = 0 to 2.0V                                                                                                                                                                    | 40   | 50   | 60   | mA     |

|                                                 |                        | V <sub>SUP1</sub> = 3.5V to 6.5V, 250mA < I <sub>FCHG</sub> < 1A                                                                                                                                | -10  |      | +10  |        |

| Fast-Charge Current<br>Accuracy                 |                        | V <sub>SUP1</sub> = 3.5V to 6.5V,<br>50mA < I <sub>FCHG</sub> < 250mA                                                                                                                           | -20  |      | +20  | %      |

| Charger Restart-Voltage<br>Threshold            |                        | Voltage drop below V <sub>CVTHR</sub> for FAST_CHR_CC to resume                                                                                                                                 |      | 200  |      | mV     |

| Soft-Start Time                                 |                        | I <sup>2</sup> C enables the charger, fast-charge current of 90% of final value; EN1B going from high to low automatically enables the charger, as long as the I <sup>2</sup> C register is set |      |      | 1    | ms     |

| BATTP Leakage Current                           | I <sub>BATTP</sub>     | Not boosting, and/or charger disabled, and/or unpowered (V <sub>BATT</sub> > V <sub>SUP1</sub> ), T <sub>A</sub> = +25°C                                                                        |      |      | 1    | μA     |

# **Electrical Characteristics (continued)**

$(V_{SUP1} = 4V, V_{SUP2} = 14V, V_{BATTP} = V_{BATTS} = 3.5V, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                 | SYMBOL             | CONDITIONS                                                                                     | MIN                        | TYP  | MAX                        | UNITS |

|-------------------------------------------|--------------------|------------------------------------------------------------------------------------------------|----------------------------|------|----------------------------|-------|

| Fast Shut-Off                             |                    | V <sub>EN1B</sub> = low to high, overrides l <sup>2</sup> C, fast-<br>charge current of < 50mA |                            |      | 5                          | μs    |

| Minimum Charger Output Capacitance        |                    | Backup battery not present                                                                     | 1                          |      |                            | μF    |

| IMON Gain                                 |                    |                                                                                                |                            | 440  |                            | A/A   |

| Thermal-Limit Temperature                 | T <sub>LIM</sub>   | Junction temperature when the charge current is reduced, $T_J$ rising                          |                            | 145  |                            | °C    |

| THERMAL OVERLOAD                          |                    |                                                                                                |                            |      |                            |       |

| Thermal-Shutdown<br>Temperature           |                    | (Note 2)                                                                                       |                            | 170  |                            | °C    |

| Thermal-Shutdown<br>Hysteresis            |                    | (Note 2)                                                                                       |                            | 20   |                            | °C    |

| BATTERY STATE-OF-HEALT                    | H CURRENT S        | INK                                                                                            |                            |      |                            |       |

| SNK Current Range                         | I <sub>SNK</sub>   | I <sup>2</sup> C control                                                                       | 0                          |      | 2                          | А     |

| SNK Current Accuracy                      |                    | I <sub>SNK</sub> = 0.5A, V <sub>BATT</sub> = 3.3V                                              | -10                        |      | +10                        | %     |

| SNK Current-Measurement Accuracy          | V <sub>AVI</sub>   | I <sub>SNK</sub> = 0.5A, V <sub>BATT</sub> = 3.3V                                              | -7.5                       | 1    | +7.5                       | %     |

| Sink Current-Measurement<br>Voltage Range | V <sub>AVI</sub>   | I <sub>SNK</sub> = 0A to 2A                                                                    | 0                          |      | 3                          | V     |

| BUB Voltage-Measurement Range             | V <sub>AVB</sub>   | V <sub>BATTS</sub> = 0 to 6V                                                                   | 0                          |      | 6                          | V     |

| Resistance of AVB<br>Pass Switch          |                    | BATT_ to AVB                                                                                   |                            |      | 10                         | Ω     |

| G2 Drive-Current Capability               | I <sub>G2</sub>    |                                                                                                | 7                          |      |                            | μA    |

| BATTS Leakage Current                     | I <sub>BATTS</sub> | T <sub>A</sub> = +25°C                                                                         |                            |      | 1                          | μΑ    |

| SNK Leakage Current                       | I <sub>SNK</sub>   | T <sub>A</sub> = +25°C                                                                         |                            |      | 1                          | μΑ    |

| G2 Output Low Voltage                     | V <sub>G2_OL</sub> | $I_{G2\_SINK} = 5\mu A$                                                                        |                            |      | -3                         | V     |

| BATTS Undervoltage<br>Threshold, Falling  |                    |                                                                                                |                            |      | 2.5                        | V     |

| DIGITAL INPUT CHARACTE                    | RISTICS (SCL,      | SDA)                                                                                           |                            |      |                            |       |

| Input High Threshold                      | V <sub>IH</sub>    | $2.5V \le V_{DDIO} \le 5.5V$                                                                   | 0.7 x<br>V <sub>DDIO</sub> |      |                            | V     |

| Input Low Threshold                       | V <sub>IL</sub>    | $2.5V \le V_{DDIO} \le 5.5V$                                                                   |                            |      | 0.3 x<br>V <sub>DDIO</sub> | V     |

| Input Threshold Hysteresis                | V <sub>HYS</sub>   |                                                                                                |                            | 0.15 |                            | V     |

| Input Leakage Current                     | I <sub>IN</sub>    | $V_{IN} = 0V \text{ or } V_{DDIO}, T_A = +25^{\circ}C$                                         |                            |      | 1                          | μΑ    |

| Input Capacitance                         | C <sub>IN</sub>    |                                                                                                |                            |      | 10                         | pF    |

| DIGITAL INPUT CHARACTE                    | RISTICS (EN1E      |                                                                                                |                            |      |                            |       |

| Input High Threshold                      | V <sub>IH</sub>    | $2.5V \le V_{BIAS} \le 5.5V$                                                                   | 1.4                        |      |                            | V     |

# **Electrical Characteristics (continued)**

$(V_{SUP1} = 4V, V_{SUP2} = 14V, V_{BATTP} = V_{BATTS} = 3.5V, T_A = T_J = -40$ °C to +125°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 1)

| PARAMETER                                        | SYMBOL               | CONDITIONS                                                                              | MIN                        | TYP                      | MAX | UNITS |

|--------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------|----------------------------|--------------------------|-----|-------|

| Input Low Threshold                              | V <sub>IL</sub>      | 2.5V ≤ V <sub>BIAS</sub> ≤ 5.5V                                                         |                            |                          | 0.5 | V     |

| Input Leakage Current                            | I <sub>IN</sub>      | V <sub>IN</sub> = 0V or V <sub>BIAS</sub> , T <sub>A</sub> = +25°C                      |                            |                          | 1   | μA    |

| DIGITAL OUTPUT CHARACT                           | TERISTICS (SDA       | A, STATUSB, BUBTRIG)                                                                    |                            |                          |     |       |

| Output High Voltage                              | V <sub>OH</sub>      | Applies only to BUBTRIG CMOS output, ISOURCE = 1mA                                      | V <sub>BIAS</sub> - 0.15   | V <sub>BIAS</sub> - 0.06 |     | V     |

| Output Low Voltage                               | V <sub>OL</sub>      | Applies to SDA, STATUSB, and BUBTRIG; I <sub>SNK</sub> = 1mA                            |                            |                          | 0.2 | V     |

| Output Inactive-Leakage<br>Current               | I <sub>OFF</sub>     | Applies only to STATUSB open-drain output (see I <sub>IN</sub> for SDA)                 |                            |                          | ±1  | μA    |

| Output Inactive Capacitance                      | C <sub>OFF</sub>     | Applies only to STATUSB open-drain output (see C <sub>IN</sub> for SDA)                 |                            |                          | 10  | pF    |

| Backup Battery-Trigger<br>Pulse Width            | t <sub>BUBTRIG</sub> | BOOST enabled and SUP2 < BOOST_OV_F                                                     | 180                        | 200                      | 220 | ms    |

| I <sup>2</sup> C-COMPATIBLE INTERFAC             | CE TIMING CHA        | RACTERISTICS (SCL, SDA)                                                                 |                            |                          |     |       |

| SCL Clock Frequency                              | f <sub>SCL</sub>     |                                                                                         | 0                          |                          | 400 | kHz   |

| Bus-Free Time Between a STOP and START Condition | t <sub>BUF</sub>     |                                                                                         | 1.3                        |                          |     | μs    |

| Hold Time for a Repeated START Condition         | t <sub>HD;STA</sub>  |                                                                                         | 0.6                        |                          |     | μs    |

| SCL Pulse Width Low                              | t <sub>LOW</sub>     |                                                                                         | 1.3                        |                          |     | μs    |

| SCL Pulse Width High                             | tHIGH                |                                                                                         | 0.6                        |                          |     | μs    |

| Setup Time for a Repeated START Condition        | t <sub>SU;STA</sub>  |                                                                                         | 0.6                        |                          |     | μs    |

| Data Hold Time                                   | t <sub>HD;DAT</sub>  |                                                                                         | 0                          |                          | 900 | ns    |

| Data Setup Time                                  | t <sub>SU;DAT</sub>  |                                                                                         | 100                        |                          |     | ns    |

| SDA and SCL Receiving<br>Rise Time               | t <sub>R</sub>       | Incoming signals (from master)                                                          | 20 +<br>C <sub>B</sub> /10 |                          | 300 | ns    |

| SDA and SCL Receiving Fall Time                  | t <sub>F</sub>       | Incoming signals (from master)                                                          | 20 +<br>C <sub>B</sub> /10 |                          | 300 | ns    |

| SDA Transmitting Fall Time                       | t <sub>F</sub>       |                                                                                         | 20 +<br>C <sub>B</sub> /10 |                          | 250 | ns    |

| Setup Time for STOP<br>Condition                 | tsu;sto              |                                                                                         | 0.6                        |                          |     | μs    |

| Bus Capacitance Allowed                          | C <sub>B</sub>       | 2.5V ≤ V <sub>DDIO</sub> ≤ 5.5V                                                         | 0                          |                          | 900 | pF    |

| Pulse Width of a<br>Suppressed Spike             |                      | Width of spikes that must be suppressed by the input filter of both SDA and SCL signals |                            | 50                       |     | ns    |

Note 1: Limits are 100% tested at  $T_A = +25$ °C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 2: Guaranteed by design; not production tested.

# **Typical Operating Characteristics (continued)**

$(V_{SUP1} = 4V, V_{SUP2} = 14V, V_{BATTP} = V_{BATTS} = 3.5V, T_A = +25$ °C, unless otherwise noted.)

AMBIENT TEMPERATURE (°C)

# **Typical Operating Characteristics (continued)**

$(V_{SUP1} = 4V, V_{SUP2} = 14V, V_{BATTP} = V_{BATTS} = 3.5V, T_A = +25$ °C, unless otherwise noted.)

www.maximintegrated.com Maxim Integrated | 10

TIME (HOURS)

SNK CURRENT (mA)

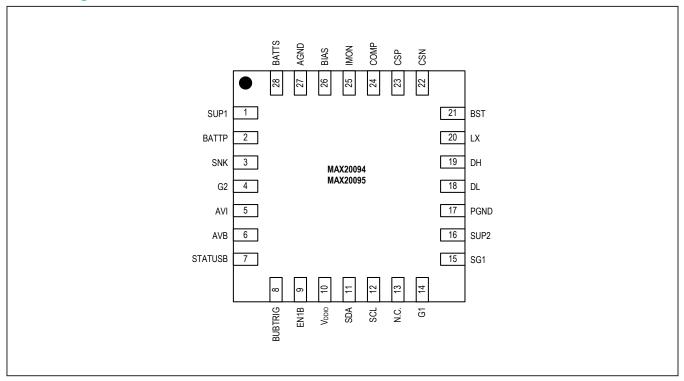

# **Pin Configuration**

# **Pin Description**

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                           |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SUP1    | Input to the CC/CV Charger. Connect a 2.2µF ceramic capacitor from SUP1 to the ground plane.                                                                                                                                                                                                       |

| 2   | BATTP   | Charger Output for the Backup Battery (BUB). BATTP is the current sink for the battery state-of-health (SOH) check. Place a 10µF, 2.2µF, and 0.1µF ceramic capacitor as close as possible to the SUP2 pin. See the <i>PCB Layout Recommendations</i> section for details on trace sizing to BATTP. |

| 3   | SNK     | Connection for the Source of the External MOSFET (M4) for State-of-Health (SOH) Measurements. The SNK pin sinks the preset current from the BUB to the external MOSFET during SOH measurements.                                                                                                    |

| 4   | G2      | Gate Drive to Turn On the MOSFET (M4) and Sink Current Into the IC. This function is controlled by I <sup>2</sup> C. G2 is not connected when the discharger is disabled. When the discharger is enabled, G2 is driven to BATTP for 62µs (typ) before the circuit starts up.                       |

| 5   | AVI     | Analog Voltage Measurement for SNK Current Set During SOH Measurement. There is a $30k\Omega$ pulldown resistor when AVI is disabled.                                                                                                                                                              |

| 6   | AVB     | Analog Battery Voltage-Measurement Output During SOH Measurements. There is a 60kΩ pulldown resistor connected 10μs before the AVB switch is turned off through I <sup>2</sup> C.                                                                                                                  |

| 7   | STATUSB | STATUSB (Battery Boost) Default Open-Drain Output. Driven to AGND during boost operation due to loss of primary power; otherwise, high impedance.                                                                                                                                                  |

| 8   | BUBTRIG | Backup Battery-Active Timed Output. Driven to BIAS for 200ms following backup boost controller start of operation; otherwise, driven to AGND.                                                                                                                                                      |

| 9   | EN1B    | Charger Disable. EN1B is connected to ground during normal operation. If pulled high, the charger is disabled, regardless of the I <sup>2</sup> C register setting.                                                                                                                                |

# Backup Battery Charger and Boost Controller

# **Pin Description (continued)**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                      |  |  |  |  |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 10  | VDDIO | I <sup>2</sup> C Logic Interface Supply Voltage, 2.5V to 5.5V. Connect to the I <sup>2</sup> C bus supply.                                                                                                                                                    |  |  |  |  |

| 11  | SDA   | C Data Signal                                                                                                                                                                                                                                                 |  |  |  |  |

| 12  | SCL   | I <sup>2</sup> C Clock Input                                                                                                                                                                                                                                  |  |  |  |  |

| 13  | N.C.  | Connect to GND in the Application                                                                                                                                                                                                                             |  |  |  |  |

| 14  | G1    | High-Side p-Channel MOSFET (M3) Driver. There is a 188kΩ resistor between G1 and SG1.                                                                                                                                                                         |  |  |  |  |

| 15  | SG1   | Source of the External p-Channel MOSFET (M3). SG1 and G1 control the gate drive of external MOSFET M3.                                                                                                                                                        |  |  |  |  |

| 16  | SUP2  | System Supply Voltage Input. High-voltage-tolerant input to the LDO, which generates 5V supply for the IC. Connect a resistor and capacitor filter from the battery-filtered rail and SUP2. See the <i>Applications Information</i> section for more details. |  |  |  |  |

| 17  | PGND  | Power Ground Pin. Connect directly to the PCB ground plane.                                                                                                                                                                                                   |  |  |  |  |

| 18  | DL    | Low-Side MOSFET Driver Output. Connect to the gate of the boost converter's low-side MOSFET.                                                                                                                                                                  |  |  |  |  |

| 19  | DH    | High-Side MOSFET Driver Output. Connect to the boost converter's high-side MOSFET.                                                                                                                                                                            |  |  |  |  |

| 20  | LX    | Switching Node of DC-DC Controller                                                                                                                                                                                                                            |  |  |  |  |

| 21  | BST   | Boosted Supply Voltage for the High-Side Sync MOSFET Gate Drive                                                                                                                                                                                               |  |  |  |  |

| 22  | CSN   | Current-Sense Resistor, Inductor-Side Sense Point. Connect CSN as close as possible to the current-sense resistor terminal. See the <i>PCB Layout Recommendations</i> section for details on proper layout.                                                   |  |  |  |  |

| 23  | CSP   | Current-Sense Resistor Input Pin. Connect CSP as close as possible to the current-sense resistor for accurate current sensing. See the <i>PCB Layout Recommendations</i> section for details on proper layout.                                                |  |  |  |  |

| 24  | COMP  | Loop-Compensation Component Connection Pin. COMP is the output of the internal g <sub>m</sub> amplifier. Connect a resistor in series with a capacitor to the AGND pin. The component values are selected according to the data sheet recommendations.        |  |  |  |  |

| 25  | IMON  | Connect IMON to GND with a 500 $\Omega$ Resistor. $V_{IMON} = (I_{CHG}/440) \times 500\Omega$ . Max $R_{IMON} = (V_{BATTP(MIN)} - 0.25)/(0.0025I_{CHG}) - 200$ .                                                                                              |  |  |  |  |

| 26  | BIAS  | Supply Pin for the Internal IC Circuits. This pin should be decoupled with a 2.2µF capacitor. BIAS is the output of the LDO connected to the V <sub>SUP</sub> pin, and is used to supply the internal circuitry with 5V.                                      |  |  |  |  |

| 27  | AGND  | Analog Ground. Low-noise ground for precision circuit blocks.                                                                                                                                                                                                 |  |  |  |  |

| 28  | BATTS | Battery Voltage-Sensing Input. Senses the battery voltage for the voltage-feedback loop and routes to the internal analog switch. Connect BATTS as close as possible to the battery's positive terminal for the most accurate voltage sensing of the battery. |  |  |  |  |

| _   | EP    | Exposed Pad                                                                                                                                                                                                                                                   |  |  |  |  |

### **Detailed Description**

The MAX20094/MAX20095 ICs combine a configurable constant-current/constant-voltage (CC/CV) battery charger, with a high-efficiency synchronous boost controller to supply critical systems in the event the primary power source is lost. In addition, diagnostic features are available to check battery state-of-health (SOH) and IC functionality. Charging thresholds and the boost output voltage are configurable to support popular battery chemistries and a wide range of cell counts. To support system integration, the ICs have an I<sup>2</sup>C slave port through which configuration and status bits can be accessed.

#### **BIAS Linear Regulator**

An internal 5V linear regulator (BIAS) generates a bias supply for the internal circuitry. Bypass BIAS with a  $2.2\mu F$  or greater ceramic capacitor to guarantee stability under the full-load condition.

The BIAS input undervoltage-lockout (UVLO) circuitry inhibits boost operation, charging, or SOH if the 5V bias supply (BIAS) is below its 2.5V (typ) UVLO falling threshold. Once the 5V bias supply (BIAS) rises above its UVLO rising threshold and the block control logic conditions are met, the ICs are functional.

#### **Block Control Logic**

The logic governing the operation of the boost controller, battery charger, and SOH is summarized in Table 1.

#### **Logic Equations**

#### **STATUSB Pin**

The STATUSB pin is an open-drain, active-low nMOS output pin that can be used in a shared-interrupt configuration with a  $\mu$ C master, and any number of similarly configured slave devices (using a wired-OR configuration with an external pullup resistor to a suitable supply, typically V<sub>DDIO</sub>). Under default conditions, the STATUSB pin is active when the boost is actively regulating SUP2. The function of the STATUSB pin can be changed to provide other types of operation using the I<sup>2</sup>C interface (see the GEN\_STATUS and EN\_INT registers).

#### **Charger Block**

The normal operating mode of the ICs is to maintain charge on the backup battery (BUB). This function is provided by the charger block.

**Table 1. Block Control Logic**

| BLOCK   | COMMENTS                                                                                                                                                                                                                    |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SOH     | SOH is enabled when:  I <sup>2</sup> C register bit is set, and Boost is not regulating, and Not in thermal-shutdown condition                                                                                              |  |  |  |

| Boost   | Boost is enabled/regulating when:  • I <sup>2</sup> C register bit is set, and  • SUP2 is below OV_F threshold  • Not in thermal-shutdown condition  Note:When boost is regulating, SOH and charger functions are disabled. |  |  |  |

| Charger | Charger is enabled when:  • I <sup>2</sup> C register bit is set and EN1B pin = 0  • Boost is not regulating, and                                                                                                           |  |  |  |

|         | <b>Note:</b> While enabled, the charger mode progression is controlled by an internal state machine and associated comparators.                                                                                             |  |  |  |

Figure 1. Charger Block Diagram

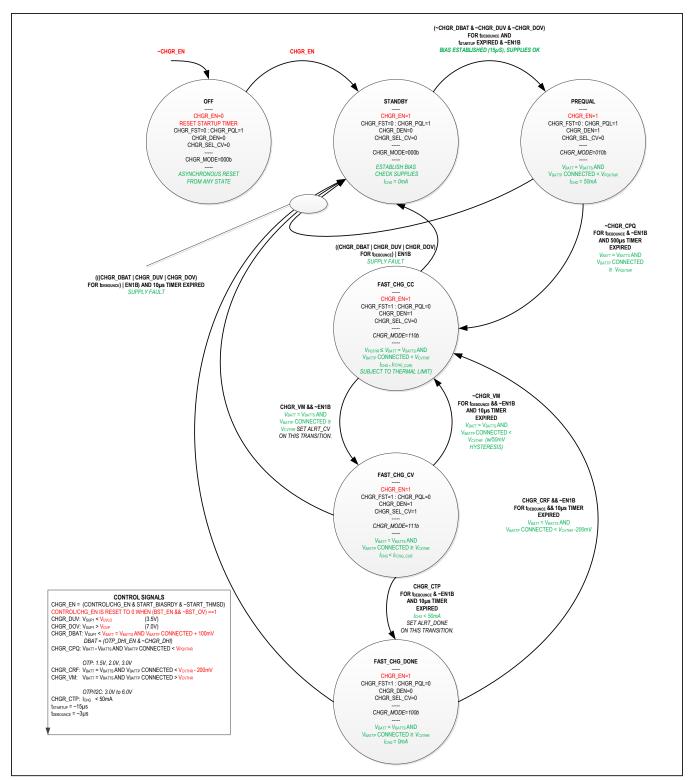

#### **Charger State Machine Description**

Once enabled, the charger operation is governed by a state machine, described below and detailed in <u>Figure 2</u>. The real-time operation of the charger can be read back using the CHGR\_STATUS (01\h) register.

The charger is held in an OFF state when CONTROL/CHG\_EN=0, or START\_BIASRDY=0, or the die temperature is above the thermal-shutdown threshold. Once CONTROL/CHG\_EN=1, bias has been established (START\_BIASRDY=1) and the die temperature is below the thermal-shutdown threshold (START\_THMSD=0), the charger moves to standby mode, and a  $15\mu S$  timer is started, allowing the charger's internal biases and comparators to settle.

The charger remains in standby mode until internal biases are established (based on the startup timer) and supply conditions are checked and found to be valid. The charger returns to standby mode in the event of an invalid supply condition. Supply conditions can be verified in real time using the CHGR\_STATUS (01\h) register. A supply condition alert is also available in GEN STATUS (02\h).

The charger next moves to a 50mA current-limited charging mode (PREQUAL). The charger remains in this mode until  $V_{BUB}$  exceeds  $V_{PQVTHR}$ , which is factory set to 2V. Contact the factory for different settings.

The charger now begins the fast-charging procedure, beginning in a constant-current mode (FAST\_CHG\_CC). Charge current is programmed using the CHGR\_CC (05\h) register. The charger remains in fast charging until VBUB exceeds VCVTHR and returns to FAST\_CHG\_CC if VBUB falls below VCVTHR, which is selected using the CHGR\_CV (06\h) register.

When  $V_{BUB}$  exceeds  $V_{CVTHR}$ , the charger continues charging in a constant-voltage mode (FAST\_CHG\_CV). A constant-voltage-mode alert is available in GEN\_STATUS (02\h), notifying the user that charging is nearing completion. Once the charger has moved to FAST\_CHG\_CV mode, the charger current is monitored. If  $I_{CHG}$  falls below 50mA, the fast-charging operation is completed and the charger moves to FAST\_CHG\_DONE mode. The charger remains in this mode until it is disabled by the user (returning to OFF), a supply fault condition occurs (returning to STANDBY), or  $V_{BUB}$  falls below  $V_{CVTHR}$  - 200mV (returning to FAST\_CHG\_CC). After entering the DONE state, a charging-done alert is available in GEN\_STATUS (02\h), notifying the user that charging is completed.

If  $V_{SUP1}$  and  $V_{BUB}$  enter dropout, the charge current is reduced due to the  $R_{DS(ON)}$  of the internal MOSFET, and the voltage difference between  $V_{SUP1}$  and the battery. If charge current continues to decrease, the ALRT\_CV and CHGR\_MODE changes to show CV state. Once charge current reduces to 50mA, ALRT\_CV remains 1, ALRT\_DONE=1, and CHGR\_MODE goes to the DONE state. Use the following equation to estimate the amount of headroom required to stay out of dropout at maximum ambient temperature:

where  $R_{CHG\ MAX}$  is the maximum value of  $R_{CHG\ from\ the\ Electrical\ Characteristics}$  table.

When CONTROL/CHG\_EN=0, then CHRG\_STATUS/SUP1\_UVLO=1. This default condition is due to internal circuitry being turned off to minimize leakage.

#### **EN1B Pin**

The EN1B pin is an active-low input port that controls the operation of the charger block. When the EN1B pin is held low, the charger operation is controlled by the I<sup>2</sup>C interface registers. When pulled high (usually due to an external system fault), the charger is instantly disabled and its internal state machine reset. The charger resumes normal operation once the pin is returned low.

Figure 2. Charger State Machine Diagram

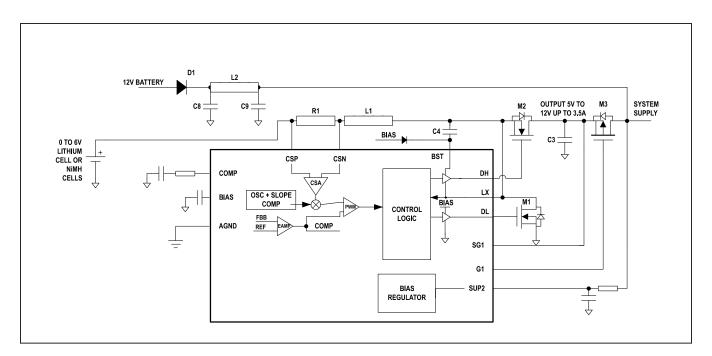

#### **Boost Block**

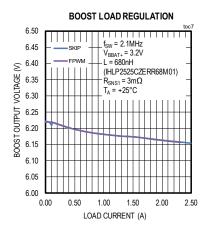

The boost block allows the ICs to maintain a regulated supply voltage on the SUP2 pin using the backup battery (BUB) in the event of a main-battery failure.

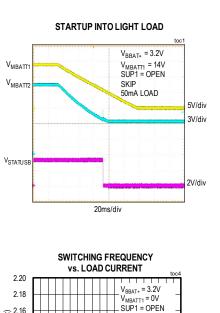

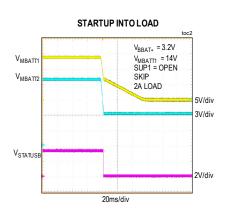

The boost is a synchronous current-mode controller with a factory-preset output voltage. The switching frequency is capable of greater than 2MHz. To enable longer battery life, the boost utilizes pulse-frequency modulation (PFM) mode at light load and automatically enters ultra-low IQ standby mode when output voltage is above the required boost voltage. The boost automatically enters awake mode when the output voltage is at or near the required boost voltage, and sends a discrete signal to the host to indicate it has awakened.

#### **Standby Current**

The ICs have low standby supply current, as mentioned in the <code>Electrical Characteristics</code> table, but still allow for 250µs (max) quick turn-on time once  $V_{SUP2}$  falls below BST\_OV\_F. I<sup>2</sup>C settings are held during the low-standby mode. In this mode, MOSFET M3 (see <code>Figure 3</code>) is OFF until the boost's overvoltage (OV) falling threshold triggers, and then it turns ON.

#### **BUBTRIG Pin**

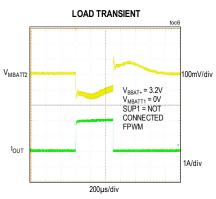

BUBTRIG is an active-low, 200ms one-shot CMOS output used to indicate the start of a period of active regulation by the boost block. When the boost is enabled and begins regulating (due to V<sub>SUP2</sub> falling below the BOOST\_OV\_F voltage threshold), BUBTRIG is asserted high for 200ms before going low again (even if the boost block continues regulation duties beyond 200ms). BUBTRIG is not asserted again unless the boost block exits active regulation mode and later resumes regulation activity.

#### **Current Limit**

A current-sense resistor ( $R_{CS}$ ), connected to the CSP and CSN pins, sets the current limit of the boost converter. The CS\_ input has a voltage trip level ( $V_{LIMIT}$ ) of 50mV (typ). The low 50mV current-limit threshold reduces the power dissipation in the current-sense resistor. Use a current-sense filter to reduce noise in the current-sense path (see the *Shunt Resistor Selection* section).

#### **Skip Operation**

Skip mode is enabled with BST\_SKIP=1. The transition from pulse-width modulation (PWM) to skip mode occurs as load current is reduced and LX current drops below zero crossing and eventually reaches  $t_{\mbox{ON MIN}}$ . Once

Figure 3. Boost Block Diagram

zero crossing and one cycle of  $t_{ON\_MIN}$  are reached, the controller enters skip mode. Transition back to PWM mode occurs when there is 480ns of  $t_{ON\_MIN}$  and the output voltage stays too low, so PWM control resumes to bring output voltage back into regulation.

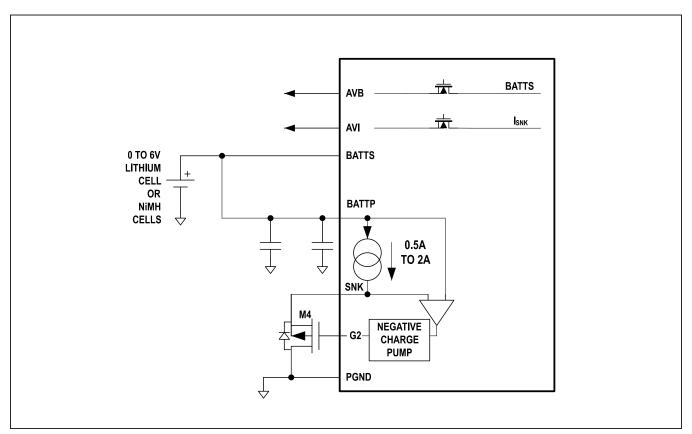

#### State-of-Health Block

The state-of-health (SOH) block (see Figure 4) allows the ICs to test the backup battery (BUB) under current-load conditions to aid in determining the condition of the BUB based on output impedance. During the test, the output voltage of the battery, as well as a voltage representation of the current applied, are made available for ADC measurements. When  $V_{BUB}$  is less than 2.5V, the SOH discharger is disabled and the SOH\_ILIM status bit is set to 1, indicating that a fault has occurred. The SOH sink current setting is the SOH (07/h) register. SOH is enabled by setting CONTROL/SOH\_EN. Selection between the

hardware-default and register-override values are set by CONTROL/SOH OVR.

#### **AVB Switch**

The AVB switch passes the BATTS sense voltage to the AVB pin. This allows voltage monitoring of the BUB. Resistance of the AVB pass switch is defined in the *Electrical Characteristics* table.

#### **AVI Switch**

The AVI switch is an analog output representing the sink current during the SOH measurement.  $V_{AVI}$  typically reads 1.5V/A of SOH current.

#### I<sup>2</sup>C Interface

Communication with the ICs is achieved using an I<sup>2</sup>C-compatible serial interface. This interface allows the user to configure and monitor the operation of the device.

Figure 4. State-of-Health Block Diagram

#### **Serial Addressing**

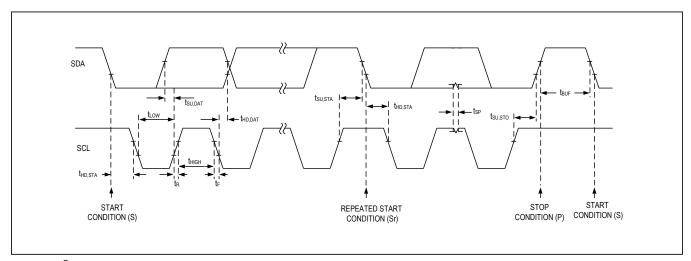

The I<sup>2</sup>C port operates as slave devices, which send and receive data through an I<sup>2</sup>C-/SMBus-compatible 2-wire serial interface. The interface uses a serial-data access (SDA) line and a serial-clock line (SCL) to achieve bidirectional communication between master(s) and slave(s) devices. A master (typically a microcontroller) initiates all data transfers to the port and generates the SCL clock that synchronizes the data transfer.

The SDA line operates as both an input and an open-drain output. The SDA line requires a pullup resistor (4.7kW, typ). The port's SCL line operates only as an input. The SCL line requires a pullup resistor (4.7kW, typ) if there are multiple masters on the 2-wire interface, or if the master in a single-master system has an open-drain SCL output.

Each transmission consists of a START (S) condition sent by a master, followed by the core's 7-bit slave address plus the NOP/W bit, one command/register byte, one data byte, and a STOP (P) condition.

#### I<sup>2</sup>C Bit Transfer

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals (see the <u>I2C START and STOP Conditions</u> section).

#### I<sup>2</sup>C START and STOP Conditions

SDA and SCL idle high when the bus is not in use. A master initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high. A START condition from the master signals the beginning of a transmission to the device. The master terminates transmission, and frees the bus, by issuing a STOP condition.

The bus remains active if a Repeated START condition is generated instead of a STOP condition; this is often used in combined-format read operations. See <u>Figure 5</u> for examples that show the generation and proper use of START (S), STOP (P), and Repeated START (Sr) conditions.

#### I<sup>2</sup>C Acknowledge

The acknowledge bit (ACK) is a clocked 9th bit the device uses for handshake receipt of each byte of data when in write mode. The device pulls down SDA during the entire master-generated 9th clock pulse if the previous byte is successfully received. Monitoring ACK allows the detection of unsuccessful data transfers that occur if a receiving device is busy, or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master retries communication. The master pulls down SDA during the 9th clock cycle to acknowledge receipt of data when the device is in read mode. An acknowledge is sent by the master after each read byte to allow data transfer to continue. A not-acknowledge (NACK) is sent when the master reads the final byte of data from the device, followed by a STOP (P) condition.

Figure 5. I<sup>2</sup>C Serial-Interface Timing Diagram

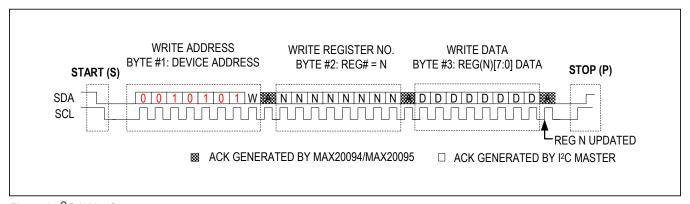

### I<sup>2</sup>C Command and Data Bytes

A command byte follows the slave address. A command byte is typically followed by one or two data bytes unless it is the last byte in the transmission, as would be the case for readback operations (see Figure 5). If data bytes follow the command byte, the command byte indicates the address of the register that should receive the data bytes that follow. The data bytes are stored in a temporary register and then transferred to the appropriate register during the ACK periods between bytes.

#### I<sup>2</sup>C Write Operations

A master device communicates with the device by transmitting the proper slave address, followed by a register/command and data word(s). Each transmit sequence is framed by a START (S) or Repeated START (Sr) condition and a STOP (P) condition. Each byte is 8 bits long and is always followed by an acknowledge (ACK) clock pulse, as shown in Figure 6. The first byte contains the

address of the device, with  $R/\overline{W} = 0$  to indicate a write. The second byte contains the register (or command) to be written, and the third byte contains the data to be written.

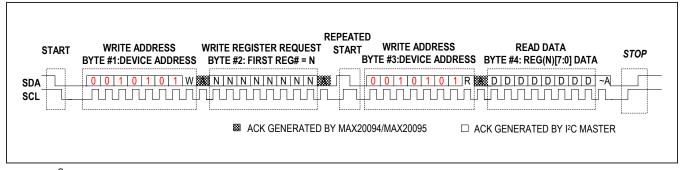

#### I<sup>2</sup>C Read Operations

The ICs support standard combined-format I $^2$ C readmode operations. Each receive sequence is again framed by a START (S) or Repeated START (Sr) condition and a STOP (P). Each byte is 8 bits long and is always followed by an ACK clock pulse, as shown in Figure 7. The first byte contains the address of the device, with R/W = 0 to indicate a write. The second byte contains the register that is to be read back. There is now a Repeated START (Sr) condition, followed by the device address, with R/W = 1 to indicate a read and an acknowledge (ACK) clock. The master still has control of the SCL line, but the device takes over the SDA line. The fourth byte in the frame contains the register data readback followed by a STOP (P) condition.

Figure 6. I<sup>2</sup>C Write Sequence

Figure 7. I<sup>2</sup>C Read Sequence

# I<sup>2</sup>C User Command and Register Map

| AD-<br>DRESS | NAME             | MSB                       | •                  |             |               |               |               |              | LSB           |

|--------------|------------------|---------------------------|--------------------|-------------|---------------|---------------|---------------|--------------|---------------|

| USER CO      | MMANDS           |                           |                    |             | l             | ı             | <u> </u>      |              |               |

| 0x00         | CHIP_ID[7:0]     |                           |                    |             | DIE_TY        | PE[7:0]       |               |              |               |

| 0x01         | CHGR_STATUS[7:0] | CHGR_<br>EN               | -   CHGR MODELY:01 |             |               | -             | SUP1_<br>UVLO | SUP1_<br>OVP | SUP1_<br>BATT |

| 0x02         | GEN_STATUS[7:0]  | BOOST                     | ALRT_<br>BST       | ALRT_<br>CV | ALRT_<br>DONE | ALRT_<br>SUP1 | THRM_<br>LIM  | THRM_<br>SD  | SOH_<br>ILIM  |

| 0x03         | EN_INT[7:0]      | EN_BST                    | EN_<br>ABST        | EN_ACV      | EN_ADN        | EN_ASP        | EN_TLIM       | EN_TSD       | EN_<br>SOHI   |

| 0x04         | CONTROL[7:0]     | SOH_EN                    | SOH_<br>OVR        | AVI_EN      | AVB_EN        | CHG_EN        | CHG_<br>IMON  | BST_EN       | BST_<br>SKIP  |

| 0x05         | CHGR_CC[7:0]     | _                         | _                  | _           |               | FC            | HG_CUR[4      | :0]          |               |

| 0x06         | CHGR_CV[7:0]     | -                         | _                  | _           | VCVTHR[4:0]   |               |               |              |               |

| 0x07         | SOH[7:0]         | ISINK[3:0] REG_ISINK[3:0] |                    |             |               |               |               |              |               |

| 0x08         | SW_RST[7:0]      | All_Zeros[7:0]            |                    |             |               |               |               |              |               |

| 0xFF         | NO_OP[7:0]       |                           |                    |             | Dont_C        | are[7:0]      |               |              |               |

## CHIP\_ID (0x00)

CHIP\_ID is a read-only register that provides information on the chip and silicon revision.

| BIT         | 7 | 6                                       | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------|---|-----------------------------------------|---|---|---|---|---|---|--|

| Field       |   | DIE_TYPE[7:0]                           |   |   |   |   |   |   |  |

| Reset       |   | 0x02 for MAX20094 and 0x03 for MAX20095 |   |   |   |   |   |   |  |

| Access Type |   | Read Only                               |   |   |   |   |   |   |  |

| BITFIELD | BITS | DESCRIPTION                                                     |

|----------|------|-----------------------------------------------------------------|

| DIE_TYPE | 7:0  | DIE_TYPE provides information on the chip and silicon revision. |

# Backup Battery Charger and Boost Controller

### CHGR\_STATUS (0x01)

CHGR\_STATUS is a read only register that provides information on the Charger operating mode and related Supply1 voltage status.

| BIT         | 7         | 6              | 5         | 4 | 3 | 2             | 1         | 0             |

|-------------|-----------|----------------|-----------|---|---|---------------|-----------|---------------|

| Field       | CHGR_EN   | CHGR_MODE[2:0] |           |   | - | SUP1_<br>UVLO | SUP1_OVP  | SUP1_<br>BATT |

| Reset       |           |                |           |   |   |               |           |               |

| Access Type | Read Only |                | Read Only |   |   | Read Only     | Read Only | Read Only     |

| BITFIELD  | BITS | DESCRIPTION                                                                                                                       |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| CHGR_EN   | 7    | 0 = Disabled: CONTROL/CHG_EN=0, or BIAS is below UVLO threshold. 1 = Enabled: CONTROL/CHG_EN=1, and BIAS is above UVLO threshold. |

| CHGR_MODE | 6:4  | 0b000 = Disabled/standby 0b010 = Prequalify-Charging Mode:                                                                        |

| SUP1_UVLO | 2    | $0 = V_{SUP1} > 3.5V$<br>$1 = V_{SUP1} < 3.5V$<br><b>Note:</b> 1 when CHG_EN=0.                                                   |

| SUP1_OVP  | 1    | $0 = V_{SUP1} < 7.0V$<br>$1 = V_{SUP1} > 7.0V$                                                                                    |

| SUP1_BATT | 0    | 0 = V <sub>SUP1</sub> > (V <sub>BATT</sub> + 100mV)<br>1 = V <sub>SUP1</sub> < (V <sub>BATT</sub> + 100mV)                        |

# Backup Battery Charger and Boost Controller

### GEN\_STATUS (0x02)

GEN\_STATUS is a read-only register that provides information on the status and operation of all internal blocks within the ICs. The contents of the GEN\_STATUS register can be individually selected for inclusion in the STATUS/INTB interupt term using the EN\_INT register.

| BIT         | 7         | 6         | 5         | 4             | 3             | 2         | 1         | 0         |

|-------------|-----------|-----------|-----------|---------------|---------------|-----------|-----------|-----------|

| Field       | BOOST     | ALRT_BST  | ALRT_CV   | ALRT_<br>DONE | ALRT_<br>SUP1 | THRM_LIM  | THRM_SD   | SOH_ILIM  |

| Reset       |           |           |           |               |               |           |           |           |

| Access Type | Read Only | Read Only | Read Only | Read Only     | Read Only     | Read Only | Read Only | Read Only |

| BITFIELD  | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOST     | 7    | 0 = Disabled: CONTROL/BST_EN = 0, or V <sub>SUP2</sub> > V <sub>BOOST_OV_F</sub> 1 = Enabled: CONTROL/BST_EN = 1 and V <sub>SUP2</sub> < V <sub>BOOST_OV_F</sub> <b>Note:</b> Boost threshold is set through OTP.                                                                                                                                                                               |

| ALRT_BST  | 6    | 0 = Boost has not been activated since the last read. 1 = Boost has been activated since last the read. Edge-Set, Clear-on-Read: Once read, this alert is cleared until the boost is deactivated and reactivated. Real-time boost activity can be monitored using D7.                                                                                                                           |

| ALRT_CV   | 5    | 0 = Charger has not reached fast-charge CV mode since the last read. 1 = Charger has reached fast-charge CV mode since the last read. Edge-Set, Clear-on-Read: Onceread, this alert is cleared until the charger exits and reenters the CV state.                                                                                                                                               |

| ALRT_DONE | 4    | 0 = Charger has not reached fast-charge-done mode since the last read. 1 = Charger has reached fast-charge-done mode since the last read. Edge-Set, Clear-on-Read: Onceread, this alert is cleared until the charger exits and reenters the done state.                                                                                                                                         |

| ALRT_SUP1 | 3    | 0 = Supply1 conditions allow normal charger operation. 1 = One or more supply status indicators is active.  Level-Set, Clear-on-Read: Once read, this alert is cleared if the supply condition has been resolved. Individual supply faults can be read back using CHGR_STATUS.                                                                                                                  |

| THRM_LIM  | 2    | 0 = Charger is not operating, or is operating normally. 1 = Charger is operating in a thermally limited (reduced-current) mode (> 135°C).  Level-Set, Clear-on-Read: Once read, this alert is cleared if the thermal-limit condition has been resolved.                                                                                                                                         |

| THRM_SD   | 1    | 0 = Device is operating normally. 1 = Device thermal protection is engaged (> 170°C).  Level-Set, Clear-on-Read: Onceread, this alert is cleared if the thermal-shut-down condition has been resolved.                                                                                                                                                                                          |

| SOH_ILIM  | 0    | 0 = SOH is not operating, or is operating normally (I <sub>SNK</sub> < 3A, or V <sub>BATTP</sub> > undervoltage threshold). 1 = SOH is operating in overcurrent condition (I <sub>SNK</sub> ≥ 3A, or V <sub>BATTP</sub> > undervoltage threshold).  Level-Set, Clear-on-Read: Once read, this alert is cleared if the overcurrent condition, or BATTP undervoltage condition has been resolved. |

### **EN\_INT (0x03)**

EN\_INT is a read/write register that governs the operation of the STATUSB output pin. The content of this register determines which interrupt input terms are included in the interrupt output OR term (e.g., a '1' in an EN\_INT register indicates that the corresponding input term is included in the STATUS interrupt output OR term). See the GEN\_STATUS register for detailed descriptions of the interrupt terms.

| BIT         | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Field       | EN_BST      | EN_ABST     | EN_ACV      | EN_ADN      | EN_ASP      | EN_TLIM     | EN_TSD      | EN_SOHI     |

| Reset       | 0b1         | 0b0         |

| Access Type | Write, Read |

| BITFIELD | BITS | DESCRIPTION                                                                                                         |

|----------|------|---------------------------------------------------------------------------------------------------------------------|

| EN_BST   | 7    | 0 = BOOST status is not included in the STATUS OR term. 1 = BOOST status is included in the STATUS OR term.         |

| EN_ABST  | 6    | 0 = ALRT_BST status is not included in the STATUS OR term. 1 = ALRT_BST status is included in the STATUS OR term.   |

| EN_ACV   | 5    | 0 = ALRT_CV status is not included in the STATUS OR term. 1 = ALRT_CV status is included in the STATUS OR term.     |

| EN_ADN   | 4    | 0 = ALRT_DONE status is not included in the STATUS OR term. 1 = ALRT_DONE status is included in the STATUS OR term. |

| EN_ASP   | 3    | 0 = ALRT_SUP1 status is not included in the STATUS OR term. 1 = ALRT_SUP1 status is included in the STATUS OR term. |

| EN_TLIM  | 2    | 0 = THRM_LIM status is not included in the STATUS OR term. 1 = THRM_LIM status is included in the STATUS OR term.   |

| EN_TSD   | 1    | 0 = THRM_SD status is not included in the STATUS OR term. 1 = THRM_SD status is included in the STATUS OR term.     |

| EN_SOHI  | 0    | 0 = SOH_ILIM status is not included in the STATUS OR term. 1 = SOH_ILIM status is included in the STATUS OR term.   |

### CONTROL (0x04)

CONTROL is a read/write register that enables/disables device features.

| BIT         | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Field       | SOH_EN      | SOH_OVR     | AVI_EN      | AVB_EN      | CHG_EN      | CHG_IMON    | BST_EN      | BST_SKIP    |

| Reset       | 0b0         | 0b1         |

| Access Type | Write, Read |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BITTILLD | ытэ  | 0 = SOH disabled, G2 driven to BATTP.                                                                                                                                                                                                                                                                                                            |