# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **General Description**

The MAX14912/MAX14913 have eight 640mA smart highside switches that can also be configured as push-pull drivers for high-speed switching. The propagation delay from input to switching of the high-side/low-side drivers is 1µs (max). Each high-side driver has a low on-resistance of 230m $\Omega$  (max) at 500mA load current at T<sub>A</sub> = 125°C.

The device is configured and controlled either through pins or the SPI interface. The SPI interface is daisy-chainable, which allows efficient cascading of multiple devices. SPI also supports command mode, for the highest detailed diagnostic information. The MAX14912 allows configuration through SPI in parallel and serial setting modes, while the MAX14913 only supports configuration through SPI in serial setting mode.

Open-load detection in high-side mode detects both open-wire conditions in the switch on/off states, and LED drivers provide indication of per-channel fault and status conditions. Internal active clamps accelerate the shutdown of inductive loads fast in high-side mode.

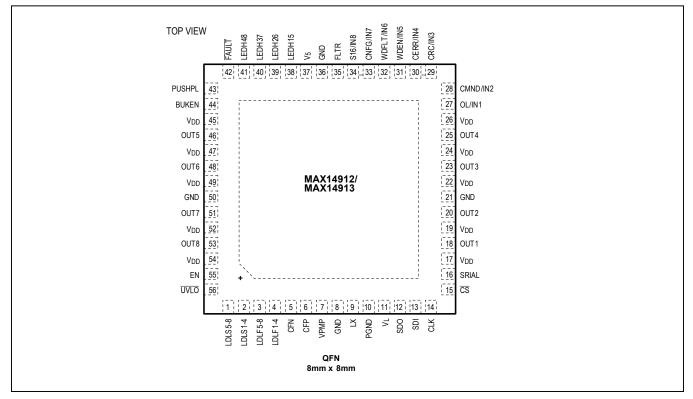

The MAX14912/MAX14913 are available in a 56-pin QFN 8mm x 8mm package.

#### **Applications**

- Industrial Digital Outputs

- PLC Systems

- Building Automation

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Low Power and Heat Dissipation

- 230mΩ (max) High-Side R<sub>ON</sub> at T<sub>A</sub> = 125°C

- High-Efficiency 5V/100mA Buck Regulator

- Fast Switching Ideal for High-Speed Control Systems

- 0.1µs (typ.) Propagation Delay (High-Side Mode)

- 0.5µs (typ.) Propagation Delay (Push-Pull Mode)

- 200kHz Switching-Rate Capability in Push-Pull Mode

- Fast Inductive Load Demagnetization

- Robust Operation

- 60V Abs Max V<sub>DD</sub> Rating

- Safe-Demagnetization: Tum-Off of Unlimited Inductance

- IEC61000-4-2 8kV Air Gap/6kV Contact ESD Protection

- +  $\pm 1kV/42\Omega$  Surge Protection with TVS on VDD

- · Robust SPI Interface with Watchdog and CRC

- -40°C to +125°C Ambient Operating Temperature Range

- Extensive Diagnostics Reduces System Downtime

- · Per Driver and Chip Thermal Shutdown

- · Open-Wire Detection in High-Side Mode

- Low Supply Voltage Warning

- Undervoltage Detection

- Overvoltage Detection on OUT

- Overcurrent Detection

- · LED Drivers for Visual Fault and Output State Indication

- Flexible Interface for Ease of Design

- Serial and/or Parallel Control Interface

- · Per-Channel Configuration and Monitoring

- Wide Logic Voltage Range (1.6V to 5.5V)

- Small Package and High Integration Enables Compact High-Density I/O Modules

- 56-Pin QFN 8mm x 8mm Package

- Eight High-Side Switches/Push-Pull Drivers

- · Daisy-Chainable SPI Interface

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Typical Application Circuit**

### Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Absolute Maximum Ratings**

| (All voltages | relative | to | GND.) |

|---------------|----------|----|-------|

|---------------|----------|----|-------|

| V <sub>DD</sub>                 | 0.3V to +60V                                          |

|---------------------------------|-------------------------------------------------------|

| PGND                            | -0.3V to +0.3V                                        |

| BUKEN, LX                       | 0.3V to (V <sub>DD</sub> + 0.3V)                      |

| V <sub>PMP</sub>                | (V <sub>DD</sub> - 0.3V) to (V <sub>DD</sub> + 6V)    |

| OUT_ (continuous voltage)       | (V <sub>DD</sub> - 49V) to (V <sub>DD</sub> + 0.3V)   |

| V <sub>5</sub> , V <sub>L</sub> | 0.3V to +6V                                           |

| CFP                             | (V <sub>DD</sub> - 0.3V) to (V <sub>PMP</sub> + 0.3V) |

| CFN                             | 0.3V to (V <sub>PMP</sub> + 0.3V)                     |

| SDO                             | 0.3V to (V <sub>L</sub> + 0.3V)                       |

| SDI, CLK, <u>CS</u>             | 0.3V to +6V                                           |

#### Package Thermal Characteristics (Note 1)

| Thermal Resistances QFN56-EP package                      |        |

|-----------------------------------------------------------|--------|

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ), |        |

| Multilayer Board                                          | 21°C/W |

| IN_, PUSHPL, FLTR, SRIAL, EN,                            |

|----------------------------------------------------------|

| FAULT, CERR/IN4, WDFLT/IN60.3V to +6V                    |

| LED_, LD0.3V to (V <sub>5</sub> + 0.3V)                  |

| Inductive Kickback Energy OUT_ pins: IL < 0.6A Unlimited |

| OUT_ Load CurrentInternally Limited                      |

| Continuous-Current (any other terminal)±100mA            |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )    |

| QFN (derate 47.6mW/°C above 70°C)                        |

| Junction TemperatureInternally Limited                   |

| Storage Temperature Range65°C to +150°C                  |

| Lead Temperature (Soldering, 10sec)+300°C                |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ), |   |

|--------------------------------------------------------|---|

| Multilayer Board1.0°C/                                 | W |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Electrical Characteristics**

$(V_{DD} = +10V \text{ to } +36V, V_5 = +4.5V \text{ to } +5.5V, V_L = +1.6V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_A = +25^{\circ}\text{C} \text{ and } V_{DD} = +24V, \text{CDCDC} = 10\mu\text{F}, \text{LDCDC} = 100\mu\text{H}, \text{CFLY} = 100\text{nF}, \text{CPUMP} = 10\mu\text{F}, \text{unless otherwise noted}.)$

| PARAMETER                                          | SYMBOL                 | CONDITIONS                                                                                               | MIN  | TYP | MAX | UNITS |

|----------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| SUPPLY                                             |                        | ·                                                                                                        |      |     |     |       |

| V <sub>DD</sub> Supply Voltage                     | V <sub>DD</sub>        |                                                                                                          | 10.5 |     | 36  | V     |

| V <sub>DD</sub> Supply Current                     | I <sub>DD</sub>        | HS mode, EN = high, OUT_<br>outputs high (no switching), no<br>load, $V_5$ and $V_L$ supplied externally |      | 1.1 | 1.5 | mA    |

|                                                    |                        | PP mode, EN = high, 100kHz switching on all OUT_, $V_5$ and $V_L$ supplied externally, no load           |      | 14  | 22  |       |

| V <sub>DD</sub> Undervoltage-Lockout<br>Threshold  | V <sub>DD_UV</sub>     | $V_5$ = 5V, $V_{DD}$ rising                                                                              | 8.5  |     | 9.5 | V     |

| V <sub>DD</sub> Undervoltage-Lockout<br>Hysteresis | V <sub>DD_UVHYST</sub> | V <sub>5</sub> = 5V                                                                                      |      | 1   |     | V     |

| V <sub>DD</sub> Low-Voltage Warning<br>Threshold   | V <sub>DD_LV</sub>     | V <sub>DD</sub> falling                                                                                  | 12   | 13  | 14  | V     |

| V <sub>DD</sub> Low-Voltage Warning<br>Hysteresis  | V <sub>DD_LVHYST</sub> | V <sub>5</sub> = 5V                                                                                      |      | 2   |     | V     |

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Electrical Characteristics (continued)**

$(V_{DD}$  = +10V to +36V,  $V_5$  = +4.5V to +5.5V,  $V_L$  = +1.6V to +5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C and  $V_{DD}$  = +24V, CDCDC = 10µF, LDCDC = 100µH, CFLY = 100nF, CPUMP = 10µF, unless otherwise noted.)

| PARAMETER                                                              | SYMBOL                        | CONDITIONS                                                                                                 | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>5</sub> /V <sub>L</sub> Supplies                                |                               | · · · · · ·                                                                                                |      |      |      |       |

| V <sub>5</sub> Supply Voltage<br>(Supplied Externally)                 | V <sub>5</sub>                |                                                                                                            | 4.5  |      | 5.5  | V     |

| V <sub>5</sub> Supply Current<br>(V <sub>5</sub> Supplied Externally)  |                               | HS mode, EN = high, OUT_<br>outputs high, no load, no LEDs<br>connected                                    |      | 2.2  | 3.2  | mA    |

|                                                                        | I <sub>V5</sub>               | PP mode, EN = high, OUT_<br>switching at 100kHz, no load, no<br>LEDs connected                             |      | 8.5  | 11   | mA    |

| V <sub>5</sub> Undervoltage-Lockout<br>Threshold                       | V <sub>V5_UV</sub>            | V <sub>DD</sub> = 24V, V5 rising                                                                           | 3.8  |      | 4.2  | V     |

| V <sub>5</sub> Undervoltage-Lockout<br>Hysteresis                      | V <sub>V5_UVHYST</sub>        | V <sub>DD</sub> = 24V                                                                                      |      | 0.3  |      | v     |

| V <sub>L</sub> Supply Voltage                                          | VL                            |                                                                                                            | 1.6  |      | 5.5  | V     |

| V <sub>L</sub> Supply Current                                          | I <sub>VL</sub>               | All logic inputs high or low                                                                               |      | 24   | 35   | μA    |

| V <sub>L</sub> Undervoltage-Lockout<br>Threshold                       | V <sub>L_UV</sub>             | V <sub>L</sub> falling                                                                                     | 1.12 | 1.27 | 1.52 | v     |

| 5V DC-DC REGULATOR                                                     | ·                             |                                                                                                            |      |      |      | •     |

| Undervoltage-Lockout<br>Threshold of the DC-DC<br>Regulator            | VDCDC_UVLO                    | V <sub>DD</sub> rising                                                                                     |      |      | 6.6  |       |

| Undervoltage-Lockout<br>Threshold of the DC-DC<br>Regulator Hysteresis | V <sub>DCDC</sub> _<br>UVLOHY |                                                                                                            |      | 0.5  |      |       |

| Output Regulated Voltage                                               | V <sub>DCDC</sub>             | 0mA to 90mA external load current                                                                          | 4.85 | 5.0  | 5.15 | V     |

| Current Limit                                                          | I <sub>CL_DCDC</sub>          |                                                                                                            | 100  |      |      | mA    |

| Turn-On Time                                                           | TON_DCDC                      | Delay from V <sub>DD</sub> crossing the<br>UVLO threshold until the DC-DC<br>regulator finishes soft-start | 3.0  | 3.4  | 3.7  | ms    |

| Switching Frequency                                                    | fDCDC                         |                                                                                                            | 540  | 600  | 660  | kHz   |

| DRIVER OUTPUTS (OUT_)                                                  |                               |                                                                                                            |      |      |      |       |

| HS Mode On-Resistance                                                  | R <sub>OUT_HS</sub>           | HS mode, HS = on, IOUT_ =<br>-500mA (Note 6)                                                               |      | 110  | 230  | mΩ    |

| HS Mode Current Limit                                                  | I <sub>LIM</sub>              | EN = high, HS = on,<br>$V_{OUT}$ = $V_{DD}$ -1V                                                            | 0.64 | 0.87 | 1.2  | A     |

| HS Mode Current-Limit V/I<br>Slope                                     |                               | (See Overcurrent and Short-Circuit<br>Protection section)                                                  |      | 150  |      | Ω     |

| HS Mode Weak Pulldown<br>Current                                       | I <sub>LKG</sub>              | High-side mode, OL detect = off,<br>HS = off, $7V < V_{OUT} < V_{DD}$                                      | 65   | 100  | 135  | μA    |

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Electrical Characteristics (continued)**

$(V_{DD}$  = +10V to +36V,  $V_5$  = +4.5V to +5.5V,  $V_L$  = +1.6V to +5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C and  $V_{DD}$  = +24V, CDCDC = 10µF, LDCDC = 100µH, CFLY = 100nF, CPUMP = 10µF, unless otherwise noted.)

| PARAMETER                                              | SYMBOL              | CONDITIONS                                                                                                                                                                     | MIN                    | TYP                  | MAX                   | UNITS |

|--------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|-----------------------|-------|

| Push-Pull Mode HS On-<br>Resistance                    | R <sub>OUT_PP</sub> | PP mode, HS = on, EN = high,<br>I <sub>OUT</sub> _ = -500mA (Note 6)                                                                                                           |                        | 110                  | 230                   | mΩ    |

| Push-Pull Mode LS On-<br>Resistance                    | V <sub>OL_PP</sub>  | PP mode, LS = on, EN = high,<br>I <sub>OUT</sub> = 500mA                                                                                                                       |                        | 1                    | 2.5                   | Ω     |

| Push-Pull Mode Current Limit                           | hur an              | PP mode, EN = High, OUT_ =<br>high, V <sub>OUT</sub> _ = V <sub>DD</sub> - 1V                                                                                                  | 0.64                   | 0.87                 | 1.2                   | А     |

|                                                        | I <sub>LIM_PP</sub> | PP mode, EN = High, OUT_ = low,<br>3V < V <sub>OUT</sub> _ < V <sub>DD</sub>                                                                                                   | 0.44                   | 0.68                 | 0.81                  | А     |

| OPEN-LOAD DETECT (OUT_)                                |                     |                                                                                                                                                                                |                        |                      |                       |       |

| Open-Load Pullup Current,<br>High-Side O <sub>ff</sub> | IOL_HSOFF           | OL detect = on, high-side mode,<br>HS = off, $7V < V_{OUT} < V_{DD} - 1V$                                                                                                      | 50                     | 74                   | 100                   | μA    |

| Open-Load Detect Threshold,<br>High-Side Off           | V <sub>OL_T</sub>   | OL detect = on, high-side mode,<br>HS = off, LED turns off/on                                                                                                                  | 6.4                    | 6.7                  | 7.35                  | V     |

| Open-Load Detect Threshold<br>Current, High-Side On    | IOL_HSON            | OL detect = on, high-side mode,<br>HS = on, $0V < V_{OUT} < (V_{DD} - 1V)$                                                                                                     | 1                      | 2                    | 3                     | mA    |

| Debounce Filter                                        | T <sub>DEB_OL</sub> | Reliable open-load detection<br>reading is obtained only if both<br>the switch input state and the load<br>level do not change for T <sub>DEB_OL</sub> ,<br>high-side = on/off |                        | 100                  |                       | ms    |

| LOGIC (I/O)                                            |                     |                                                                                                                                                                                |                        |                      |                       |       |

| Innut Voltage Lligh                                    | N                   | V <sub>L</sub> < 2.5V                                                                                                                                                          | 0.8 x V <sub>L</sub>   |                      |                       | V     |

| Input Voltage High                                     | VIH                 | V <sub>L</sub> ≥ 2.5V                                                                                                                                                          | 0.7 x V <sub>L</sub>   |                      |                       | v     |

|                                                        | Ň                   | V <sub>L</sub> < 2.5V                                                                                                                                                          |                        |                      | 0.16 x V <sub>L</sub> | V     |

| Input Voltage Low                                      | VIL                 | V <sub>L</sub> ≥ 2.5V                                                                                                                                                          |                        |                      | 0.3 x V <sub>L</sub>  | v     |

| Input Threshold Hysteresis                             | VIHYST              |                                                                                                                                                                                |                        | 0.1 x V <sub>L</sub> |                       | V     |

| Input Pulldown Resistor                                | RI                  | All logic input pins, except $\overline{CS}$ (Note 2)                                                                                                                          | 140                    | 200                  | 275                   | kΩ    |

| Input Pullup Resistor                                  | RI                  | CS input (Note 2)                                                                                                                                                              | 140                    | 200                  | 275                   | kΩ    |

| Output Logic-High (SDO)                                | V <sub>OH</sub>     | I <sub>L</sub> = -5mA                                                                                                                                                          | V <sub>L</sub> - 0.33\ | /                    |                       | V     |

| Output Logic-Low                                       | V <sub>OL</sub>     | I <sub>L</sub> = +5mA                                                                                                                                                          |                        |                      | 0.33                  | V     |

| SDO Pulldown Resistor                                  | R <sub>L_SDO</sub>  | CS = high                                                                                                                                                                      | 140                    | 200                  | 275                   | kΩ    |

| OPEN-DRAIN OUTPUTS (FAU                                | LT, CERR/IN4, W     | /DFLT/IN6)                                                                                                                                                                     |                        |                      |                       |       |

| Output Logic-Low                                       | V <sub>ODL</sub>    | I <sub>L</sub> = +5mA                                                                                                                                                          |                        |                      | 0.58                  | V     |

| Leakage                                                | I <sub>ODL</sub>    | Open-drain output off, pins are at 5.5V                                                                                                                                        | -1                     |                      | +1                    | μA    |

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Electrical Characteristics (continued)**

$(V_{DD}$  = +10V to +36V,  $V_5$  = +4.5V to +5.5V,  $V_L$  = +1.6V to +5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C and  $V_{DD}$  = +24V, CDCDC = 10µF, LDCDC = 100µH, CFLY = 100nF, CPUMP = 10µF, unless otherwise noted.)

| PARAMETER                               | SYMBOL                  | CONDITIONS                                                   | MIN                  | TYP  | MAX  | UNITS |

|-----------------------------------------|-------------------------|--------------------------------------------------------------|----------------------|------|------|-------|

| LED DRIVERS (LEDH_, LDL_)               |                         |                                                              | •                    |      |      |       |

| Output Voltage High                     | V <sub>OH_LED</sub>     | LEDH = on, I <sub>LED</sub> = 5mA                            | V <sub>5</sub> - 0.3 |      |      | V     |

| Output Leakage Current High             | I <sub>LH</sub>         | LEDH_ = off, V = 0V                                          | -50                  |      |      | μA    |

| Output Voltage Low                      | V <sub>OL_LED</sub>     | LDL = on, I <sub>LED</sub> = 5mA                             |                      |      | 0.3  | V     |

| Output Leakage Current Low              | ILL                     | LDL = off, V = 5V                                            |                      |      | 50   | μA    |

| LED Driver Scan Rate                    | FLED                    | Update rate for each LED                                     | 1.07                 | 1.18 | 1.31 | kHz   |

| Fault-LED Minimum On-Time               | <sup>t</sup> FAULT_ON   | Fault LED is turned on for at least<br><sup>t</sup> FAULT_ON |                      | 200  |      | ms    |

| PROTECTION                              |                         |                                                              |                      |      |      |       |

| OUT_ Clamp Negative<br>Voltage          | V <sub>CL</sub>         | Relative to V <sub>DD</sub> . EN = high                      | 49                   | 56   | 64.5 | V     |

| Channel Thermal-Shutdown<br>Temperature | T <sub>JSHDN</sub>      | Junction temperature rising. Per channel                     |                      | 167  |      | °C    |

| Channel Thermal-Shutdown<br>Hysteresis  | T <sub>JSHDN_HYST</sub> |                                                              |                      | 17   |      | °C    |

| Chip Thermal Shutdown                   | T <sub>CSHDN</sub>      | Temperature rising                                           |                      | 150  |      | °C    |

| Chip Thermal-Shutdown<br>Hysteresis     | T <sub>CSHDN_HYST</sub> |                                                              |                      | 8    |      | °C    |

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **AC Electrical Characteristics**

$(V_{DD} = +10V \text{ to } +36V, V_5 = +4.5V \text{ to } +5.5V, V_L = +1.6V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted}.$  Typical values are at T\_A = +25^{\circ}\text{C} and V\_{DD} = +24V, CDCDC = 10 \mu\text{F}, LDCDC = 100 \mu\text{H}, CFLY = 100n\text{F}, CPUMP = 10 \mu\text{F}, \text{ unless otherwise noted}.

| PARAMETER                               | SYMBOL                | CONDITIONS                                                                                                                                                                          | MIN  | TYP  | MAX | UNITS |

|-----------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-------|

| OUT_OUTPUTS                             |                       |                                                                                                                                                                                     |      |      |     |       |

| Power-Up Delay                          | <sup>t</sup> POWERUP  | $      EN = high time from V_{DD} > V_{DD_UV} \\       to switches turned-on, V_{HVBUCKEN} \\       = 0V or V_{DD} $                                                                |      | 5.5  |     | ms    |

| Enable Delay                            | t <sub>ENABLE</sub>   | All power supplies above UVLO<br>thresholds; time from EN positive<br>edge to switches turned on                                                                                    |      | 0.1  |     | μs    |

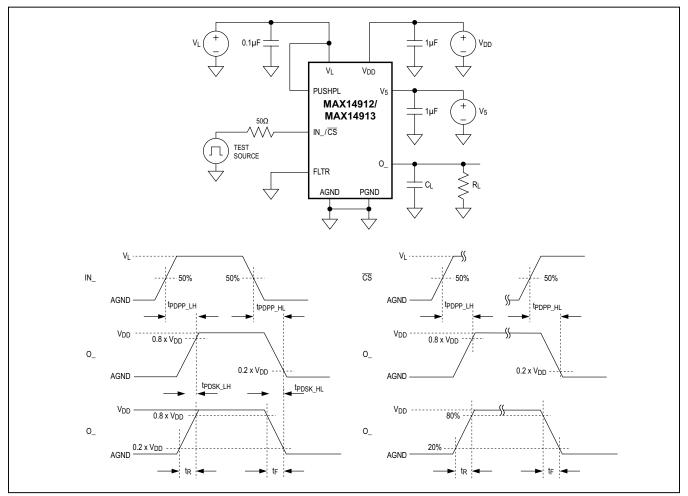

| Push-Pull Switchover Delay              | <sup>t</sup> D_PPMODE | Delay from high-side to push-pull switchover                                                                                                                                        |      | 45   |     | μs    |

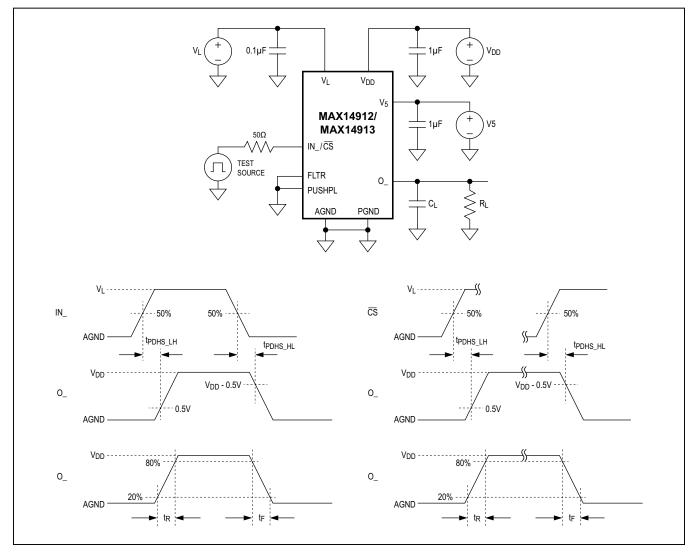

|                                         |                       | High-side mode, delay from IN_ or positive $\overline{CS}$ edge to OUT_ to 0.8 x V <sub>DD</sub> . C <sub>L</sub> = 100pF, FLTR = low.                                              |      | 0.35 | 0.7 | μs    |

| Output Propagation Delay LH             | <sup>t</sup> PD_LH    | Push-pull mode, delay from IN_ or<br>$\overline{CS}$ positive edge to OUT_ rising to<br>0.8 x V <sub>DD</sub> . C <sub>L</sub> = 100pF, FLTR = low<br>(Figure 2)                    |      | 0.40 | 0.7 |       |

|                                         |                       | High-side mode, delay from IN_<br>negative edge or $\overline{CS}$ switching high<br>to OUT_ falling by 0.5V. RL = 48 $\Omega$ ,<br>FLTR = low (Figure 1, Note 5)                   |      | 0.1  |     |       |

| Output Propagation Delay HL             | <sup>t</sup> PD_HL    | Push-pull mode, delay between IN_<br>switching low or $\overline{CS}$ switching high<br>to OUT_ falling to 0.2 x V <sub>DD</sub> . C <sub>L</sub> =<br>100pF, FLTR = low (Figure 2) |      | 0.35 | 0.7 | - µs  |

| Output-to-Output Propagation<br>Skew LH | <sup>t</sup> PD_SK_LH | Push-pull modes, C <sub>L</sub> = 1nF,<br>FLTR = X (Note 3, Note 7)                                                                                                                 | -100 | 0    | 100 | ns    |

| Output-to-Output Propagation<br>Skew HL | <sup>t</sup> PD_SK_HL | Push-pull modes, $R_L = 5k\Omega$ ,<br>$C_L = 1nF$ , FLTR = X (Note 7)                                                                                                              | -100 | 0    | 100 | ns    |

| Output Rise Time                        | t <sub>R</sub>        | Push-pull mode, 20% to 80% $V_{DD}$ , C <sub>L</sub> = 100pF, FLTR = X (Note 7)                                                                                                     |      | 0.3  |     | μs    |

|                                         |                       | High-side mode, 20% to 80%<br>V <sub>DD</sub> , FLTR = X (Note 7)                                                                                                                   |      | 0.3  |     | μs    |

| Output Fall Time                        | t <sub>F</sub>        | Push-pull mode, 80% to 20% $V_{DD}$ ,<br>V <sub>DD</sub> < 30V, C <sub>L</sub> = 100pF,<br>FLTR = X (Note 7)                                                                        |      | 0.05 |     |       |

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **AC Electrical Characteristics (continued)**

$(V_{DD} = +10V \text{ to } +36V, V_5 = +4.5V \text{ to } +5.5V, V_L = +1.6V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted}.$  Typical values are at T\_A = +25^{\circ}\text{C} and V\_{DD} = +24V, CDCDC = 10 \mu\text{F}, LDCDC = 100 \mu\text{H}, CFLY = 100n\text{F}, CPUMP = 10 \mu\text{F}, unless otherwise noted}.

| PARAMETER                          | SYMBOL                | CONDITIONS                                                                                         | MIN | TYP  | MAX | UNITS |

|------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| CRC ERROR DETECTION (C             | ERR/IN4)              |                                                                                                    |     |      |     |       |

| Propagation Dolay                  | <sup>t</sup> PDL_CERR | SRIAL = high, CRC/IN3 = high,<br>OUT_detects a CRC error on SDI<br>data, I <sub>SOURCE</sub> = 5mA |     | 14.5 |     | ns    |

| Propagation Delay                  | <sup>t</sup> PDH_CERR | SRIAL = high, CRC/IN3 = high,<br>OUT_clears/CERR/IN4,<br>I <sub>SOURCE</sub> = 5mA                 |     | 17   |     | ns    |

| WATCHDOG TIMER                     |                       |                                                                                                    |     |      |     |       |

| Watchdog Timeout Accuracy          | twd_acc               | SRIAL = high, WDEN/IN5 = high.<br>See Table 5 for watchdog timeout<br>selection.                   | -10 |      | +10 | %     |

| GLITCH FILTERS                     |                       |                                                                                                    |     |      |     |       |

|                                    |                       | FLTR = high, on EN, CS, _IN_ pins                                                                  |     |      | 80  |       |

| Pulse Length of Rejected<br>Glitch | <sup>t</sup> FPL_GF   | FLTR = X, SRIAL and PUSHPL pins                                                                    |     |      | 170 | ns    |

|                                    |                       | FLTR = high, on EN, CS, _IN_ pins                                                                  | 260 |      |     |       |

| Passes Pulse Length                | <sup>t</sup> FD_GF    | FLTR = X, SRIAL and PUSHPL pins                                                                    | 550 |      |     | ns    |

|                                    |                       | FLTR = high, on EN, CS, _IN_ pins                                                                  |     | 140  |     | 1     |

| Glitch Filter Delay Time           | <sup>t</sup> D_GF     | FLTR = X, SRIAL and PUSHPL pins                                                                    |     | 320  |     | ns    |

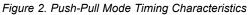

| SPI TIMING CHARACTERIST            | ics                   |                                                                                                    |     |      |     |       |

| $2.5 V \leq V_{L} < 5.5 V$         |                       |                                                                                                    |     |      |     |       |

| CLK Clock Period                   | t <sub>CH+CL</sub>    |                                                                                                    | 50  |      |     | ns    |

| CLK Pulse-Width High               | tсн                   |                                                                                                    | 10  |      |     | ns    |

| CLK Pulse-Width Low                | t <sub>CL</sub>       |                                                                                                    | 10  |      |     | ns    |

| CS Fall-to-CLK Rise Time           | t <sub>CSS</sub>      | FLTR = low (Note 5)                                                                                | 12  |      |     | ns    |

|                                    | 4055                  | FLTR = high                                                                                        | 260 | _    |     | 113   |

| SDI Hold Time                      | t <sub>DH</sub>       |                                                                                                    | 5   |      |     | ns    |

| SDI Setup Time                     | t <sub>DS</sub>       |                                                                                                    | 5   |      |     | ns    |

| Output Data Propagation<br>Delay   | t <sub>DO</sub>       | C <sub>L</sub> = 10pF. CLK falling-edge to<br>SDO stable                                           |     |      | 30  | ns    |

| SDO Rise-and-Fall Times            | t <sub>FT</sub>       |                                                                                                    |     | 1    |     | ns    |

| CS Hold Time                       | <sup>t</sup> csн      |                                                                                                    | 40  |      |     | ns    |

| CS Pulse Width High                | toopur                | FLTR = low (Note 5).                                                                               | 15  |      |     | ne    |

|                                    | tCSPW                 | FLTR = high                                                                                        | 260 |      |     | ns    |

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **AC Electrical Characteristics (continued)**

$(V_{DD} = +10V \text{ to } +36V, V_5 = +4.5V \text{ to } +5.5V, V_L = +1.6V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$  and  $V_{DD} = +24V$ , CDCDC = 10µF, LDCDC = 100µH, CFLY = 100nF, CPUMP = 10µF, unless otherwise noted.

| PARAMETER                        | SYMBOL             | CONDITIONS                                               | MIN | ТҮР | MAX | UNITS |

|----------------------------------|--------------------|----------------------------------------------------------|-----|-----|-----|-------|

| 1.6V ≤ V <sub>L</sub> < 2.5V     |                    |                                                          | •   |     |     |       |

| CLK Clock Period                 | t <sub>CH+CL</sub> |                                                          | 60  |     |     | ns    |

| CLK Pulse-Width High             | t <sub>CH</sub>    |                                                          | 13  |     |     | ns    |

| CLK Pulse-Width Low              | t <sub>CL</sub>    |                                                          | 13  |     |     | ns    |

|                                  |                    | FLTR = low (Note 5)                                      | 15  |     |     | ns    |

| CS Fall to CLK Rise Time         | tcss               | FLTR = high                                              | 260 |     |     |       |

| SDI Hold Time                    | t <sub>DH</sub>    |                                                          | 10  |     |     | ns    |

| SDI Setup Time                   | t <sub>DS</sub>    |                                                          | 10  |     |     | ns    |

| Output Data Propagation<br>Delay | t <sub>DO</sub>    | C <sub>L</sub> = 10pF. CLK falling-edge to<br>SDO stable |     |     | 40  | ns    |

| SDO Rise-and-Fall Times          | t <sub>FT</sub>    |                                                          |     | 2.5 |     | ns    |

| CS Hold Time                     | t <sub>CSH</sub>   |                                                          | 40  |     |     | ns    |

| CS Pulse-Width High              | t <sub>CSPW</sub>  | FLTR = low (Note 5)                                      | 20  |     |     | ns    |

**Note 2:** All units are production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design.

**Note 3:** Channel-to-channel skew is defined as the difference in propagation delays between channels on the same device with the same polarity.

**Note 4:** All logic input pins except  $\overline{CS}$  have a pulldown resistor.  $\overline{CS}$  has a pullup resistor.

Note 5: Specification is guaranteed by design; not production tested.

Note 6: Excludes bond wire resistance.

Note 7: X - means do not care.

#### **ESD Characteristics**

| PARAMETER | SYMBOL           | CONDITIONS                       | MIN | TYP | MAX | UNITS |

|-----------|------------------|----------------------------------|-----|-----|-----|-------|

|           | V <sub>ESD</sub> | OUT_ pins. Contact (Note 6)      |     | ±8  |     | kV    |

| ESD       |                  | OUT_ pins. Air Discharge         |     | ±15 |     | kV    |

|           |                  | All other pins. Human Body Model |     | ±2  |     | kV    |

**Note 6:** Bypass each V<sub>DD</sub> pin to AGND with a 1µF capacitor as close as possible to the device for high-ESD protection.

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Test Circuits/Timing Diagrams**

Figure 1. High-Side Mode Timing Characteristics

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Test Circuits/Timing Diagrams (continued)**

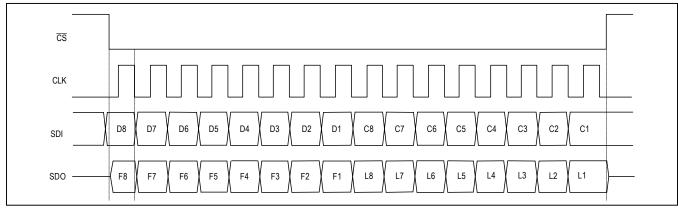

Figure 3. SPI Timing Diagram

# Octal High-Speed, High-Side Switch/Push-Pull Driver

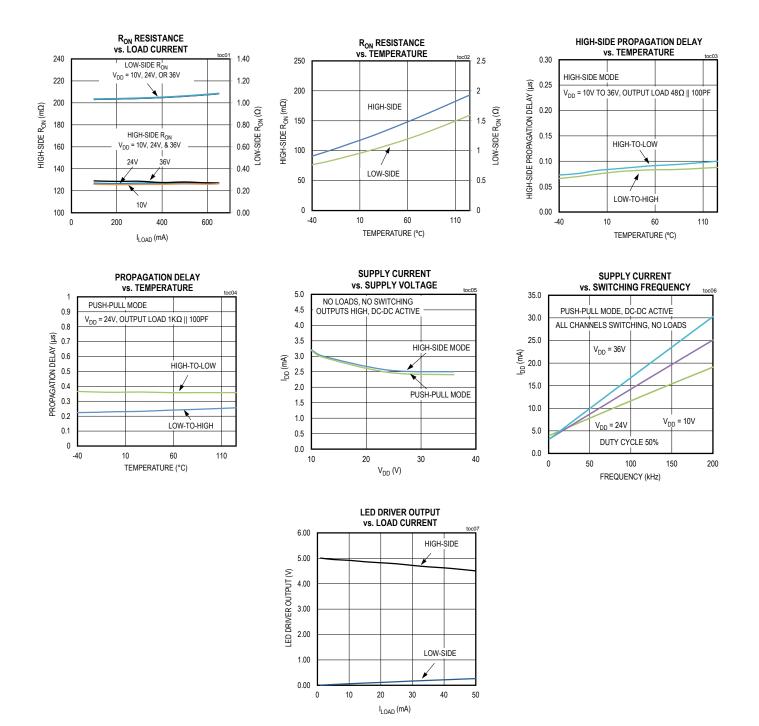

#### **Typical Operating Characteristics**

(V<sub>DD</sub> = 24V; V<sub>5</sub> = 5V, V<sub>L</sub> = 3.3V, T<sub>A</sub> = +25°C, unless otherwise noted.)

# Octal High-Speed, High-Side Switch/Push-Pull Driver

### **Pin Configuration**

#### **Pin Description**

| PIN           | NAME                                    | FUNCTION                                                                                                                                                  |

|---------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED DRIVERS   |                                         |                                                                                                                                                           |

| 1, 2          | LDLS5-8,<br>LDLS1-4                     | Status LED Cathode Outputs (Open-Drain Low-Side)                                                                                                          |

| 3, 4          | LDLF5-8,<br>LDLF1-4                     | Fault LED Cathode Outputs (Open-Drain Low-Side)                                                                                                           |

| 38–41         | LEDH15,<br>LEDH26,<br>LEDH37,<br>LEDH48 | LED Anode Connections (Open-Drain High-Side). Connect a resistor in series to set the diode current.                                                      |

| POWER SUPPI   | LY                                      |                                                                                                                                                           |

| 5             | CFN                                     | Charge-Pump Flying Capacitor                                                                                                                              |

| 6             | CFP                                     | Charge-Pump Flying Capacitor. Connect a 200nF/50V capacitor to CFN.                                                                                       |

| 7             | VPMP                                    | Charge-Pump Output. Connect a $10\mu$ F/5V capacitor between VPMP and V <sub>DD</sub> . VPMP is not intended for use as a power supply for other devices. |

| 8, 21, 36, 50 | GND (4x)                                | Ground. Connect all GND pins together.                                                                                                                    |

| 9             | LX                                      | DC-DC Converter Switching Output. Connect LX to the switching-side of the inductor.                                                                       |

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### PIN NAME FUNCTION PGND 10 Ground for the DC-DC Converter. Connect to GND. Logic Supply Input. V1 defines the levels on all I/O logic interface pins. Bypass V1 to DGND VL 11 through a 100nF ceramic capacitor. 17, 19, 22, 24, Supply Voltage, Nominally 24V. Connect all VDD together. Bypass VDD to GND through a 1µF 26, 45, 47, 49, V<sub>DD</sub> (10x) capacitor. 52, 54 5V Supply Input. V<sub>5</sub> can be powered by an external 5V supply or the internal 5V buck. Bypass 37 $V_5$ V<sub>5</sub> to DGND through a 10µF ceramic capacitor. Enable Input for Buck Regulator. BUKEN should be permanently connected to either VDD or 44 BUKEN GND-do not switch BUKEN. Connect BUKEN to GND if not using the internal buck. Connect BUKEN to V<sub>DD</sub> to use the internal buck. UVLO UVLO is an Open-Drain, Undervoltage Indicator of the V<sub>DD</sub> Supply. 56 SERIAL INTERFACE 12 SDO Serial-Data Output. SPI MISO data output to controller. SDI Serial-Data Input. SPI MOSI data from controller. 13 14 CLK Serial-Clock Input from SPI Controller CS 15 Chip-Select Input from Controller LOGIC INTERFACE Serial/Parallel Select Input. Drive SRIAL high to set the MAX14912/MAX14913 outputs through 16 SRIAL the serial interface. Drive SRIAL low to set the MAX14912/MAX14913outputs through the parallel ( /IN) pins. SRIAL does not affect serial readback of diagnostic/status information. Open-Load Select Input/IN1 Input. In serial mode (SRIAL = high), drive OL/IN1 = high to enable OL/IN1 27 open-load detection on all eight OUT\_ outputs when in high-side operation. In parallel mode (SRIAL = low), OL/IN1 sets OUT1 on/off/high/low. Command Mode SPI Input/IN2 Logic Input. In serial mode (SRIAL = high), CMND/IN2 enables CMND/IN2 28 command-based SPI access (see Detailed Description section for details). In parallel mode (SRIAL = low), CMND/IN2 sets OUT2 on/off/high/low. CRC Select Input/IN3 Input. In serial mode (SRIAL = high), drive CRC/IN3 = high to enable CRC 29 CRC/IN3 error detection on serial data. In parallel mode (SRIAL = low), CRC/IN3 sets OUT3 on/off/high/ low. CRC Error Detection Output/IN4 Input. In serial mode (SRIAL = high) with error checking enabled (CRC/IN3 = high), CERR/IN4 is an open-drain output whose transistor turns on when 30 CERR/IN4 the device detects an error on SDI data. In parallel mode (SRIAL = low), CERR/IN4 sets OUT4 on/off/high/low. Watchdog Enable Input/ IN5 Input. In serial mode (SRIAL= high), WDEN/IN5 enables the 31 WDEN/IN5 watchdog timer. In parallel mode (SRIAL= low), WDEN/IN5 sets OUT5 on/off/high/low. Watchdog Fault Output/IN6 Input. In serial mode (SRIAL = high), WDFLT/IN6 is the open-drain WDFLT/IN6 watchdog fault output, which turns on when a watchdog fault is detected while WDEN/IN5 is 32 high. In parallel mode (SRIAL = low), WDFLT/IN6 sets OUT6 on/off/high/low.

#### **Pin Description (continued)**

# Octal High-Speed, High-Side Switch/Push-Pull Driver

### **Pin Description (continued)**

| PIN                               | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33                                | CNFG/IN7  | Configure Input/IN7 Input. In serial mode (SRIAL = high), drive CNFG/IN7 high to enable per-<br>channel configuration through the serial interface. In serial mode, drive CNFG/IN7 low to allow<br>setting the OUT_ outputs through the serial interface. In parallel mode (SRIAL = low), CNFG/IN7<br>sets OUT7 on/off/high/low. |

| 34                                | S16/IN8   | 16-Bit Serial Select/IN8 Input.<br>In serial mode (SRIAL = high), drive S16/IN8 high to select 16-bit serial-interface operation.<br>Drive S16/IN8 low in serial mode for 8-bit serial operation.<br>In parallel mode (SRIAL = low), S16/IN8 sets OUT8 on/off/high/low.                                                          |

| 35                                | FLTR      | Glitch Filter Enable Input. Set FLTR high to enable glitch filtering on all parallel logic inputs and $\overline{CS}$ .                                                                                                                                                                                                          |

| 42                                | FAULT     | Open-Drain Fault Output. The FAULT transistor turns on low when a fault condition (driver shutdown or open-load detect) occurs.                                                                                                                                                                                                  |

| 43                                | PUSHPL    | Push-Pull, High Slew-Rate Configuration Input. When PUSHPL is set high, all OUT_pins operate in push-pull mode. When PUSHPL is set low, all OUT_pins operate in high-side mode.                                                                                                                                                  |

| 55                                | EN        | Output Enable Input. Driving EN low turns all high-side OUT_ switches off, and three-states all push-pull OUT_ drivers and turns all LED drivers off. Driving EN high enables normal operation.                                                                                                                                  |

| SWITCH/DRIVE                      | R OUTPUTS |                                                                                                                                                                                                                                                                                                                                  |

| 18, 20, 23, 25,<br>46, 48, 51, 53 | OUT1–OUT8 | Driver Output N. May be configured as a high-side switch or push-pull output.                                                                                                                                                                                                                                                    |

# Octal High-Speed, High-Side Switch/Push-Pull Driver

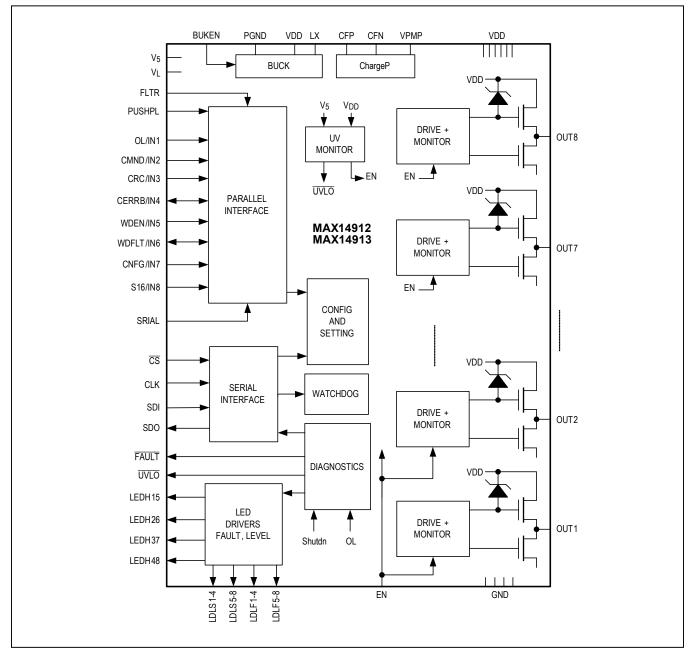

#### Functional (or Block) Diagram

### Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Detailed Description**

#### High-Side Mode

The high-side drivers (HS) have  $230m\Omega$  (max) on-resistance when sourcing 500mA at  $T_A = +125^{\circ}C$ . The OUT\_ output voltage can go below ground, as can occur during inductive load turn-off/demagnetization. Internal clamping diodes limit the negative excursion to ( $V_{DD} - V_{CL}$ ) and allow free-wheeling currents to demagnetize the inductive loads quickly.

Low-side transistors (LS) can be switched in to provide push-pull operation. Fast discharge of ground-connected RC loads is achieved by push-pull drive. In push-pull mode, the OUT\_ outputs are clamped to GND.

#### **Output Parallelization**

The devices support paralleling of channels in high-side mode to provide higher current. The channels can be paired (1-2, 3-4, 5-6, and 7-8) by setting two bits of the SPI register 3: joinUP and joinDW (see Table 6).

When joinDW = 1, OUT1 and OUT2 are connected together, and OUT3 and OUT4 are connected together, and:

- Input signals related to channels 2 and 4 are neglected;

- Output status is determined by inputs 1 and 3;

- Push-pull mode is disabled.

When joinUP = 1, OUT5 and OUT6 are connected together, and OUT7 and OUT8 are connected together, and:

- Input signals related to channels 6 and 8 are neglected;

- Output status is determined by inputs 5 and 7;

- Push-pull mode is disabled.

The above configuration can be used without any additional external zener clamping.

Besides pairing of drivers through internal configuration, multiple OUTs can be operated in parallel by tying the OUT\_ together and driving the inputs simultaneously. In this case, an external zener clamp is required per output set for quenching the energy during inductive load turnoff. The external clamp voltage of this zener diode must be lower than the minimum internal clamp voltage ( $V_{CL}$ (min)). The reason is that there is channel-to-channel variation between the internal clamp voltages. Without an external zener diode, during turn-off of channels connected in parallel, the internal clamp with the lowest clamp voltage turns on and dissipates all the energy.

Channel diagnostics for fault detection remains independent in case of paralleling the outputs.

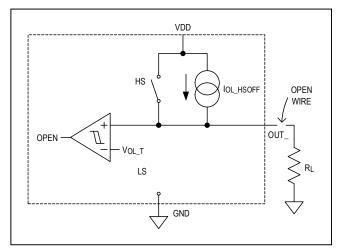

#### **Open-Load/Wire Detection**

Detection of an open-load condition can be enabled on a per-channel basis through serial configuration, or globally in serial mode through the OL/IN1 input. Open-load detection works in high-side mode only. It operates with the HS driver either on or off.

When the HS switch is off, a current source is enabled, which pulls OUT\_ to  $V_{DD}$  when the wire is open. If the OUT\_ voltage is above  $V_{OL}$  \_\_\_\_\_, an open load is signaled.

When the HS switch is on, the voltage across the HS switch is monitored. If this drop is below a load current of  $I_{OL}$  HSON, an open-load fault is reported.

The switch input state and the load condition must both be stable for at least  $t_{DEB}$  OL to get a reliable reading.

When an open-load condition is detected on an output:

- 1) The F\_ bit is set for that output in the serial diagnostic data.

- 2) The fault LED is turned on for at least 200ms for that channel.

- 3) The open-drain global FAULT transistor is turned on for at least 200ms.

Figure 4. Open-Wire Load Detection

### Octal High-Speed, High-Side Switch/Push-Pull Driver

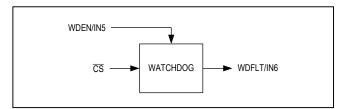

#### Watchdog

The watchdog timer allows monitoring activity on the  $\overline{CS}$  input in serial mode (SRIAL = high). Drive WDEN/IN5 high to enable the watchdog function. The watchdog monitors and expects activity on the  $\overline{CS}$  input. The WD timer is reset at every  $\overline{CS}$  falling edge. If the timer is not reset after the timeout delay, see <u>Table 8</u>), all OUT\_ outputs are turned off and the watchdog fault output (WDFLTB/IN6) transitions low until the next  $\overline{CS}$  falling edge.

The watchdog timeout can be selected in SPI command mode (see the <u>Configuration and Monitoring</u> section). Bits selection in Register 3: WD[1:0] = 00 for 0.9s, WD[1:0] = 01 for 0.45s and WD[1:0] = 10 for 0.15s. The default value is 0.9s.

#### **Thermal Management**

Every driver's temperature is constantly monitored while  $V_{DD} > V_{DD\_UV}$ . If the temperature of a driver rises above the thermal-shutdown threshold of  $T_{JSHDN}$ , that channel is automatically turned off for protection. The drivers are turned on again once the temperature drops by a hysteresis margin of  $T_{JSHDN\_HYST}$ .

Both high and low-side drivers are thermally protected with a per-driver protection circuit.

When a driver turns off due to thermal shutdown:

- 1) A fault is indicated through the global FAULT output.

- The F\_ bit of that channel is set in the diagnostic byte in the SPI interface.

- 3) The fault LED driver turns on for that channel.

The device also has a chip thermal shutdown that triggers a FAULT output and all the channels shut down if the temperature rises above  $T_{CSHDN}$ .

#### **Overcurrent and Short-Circuit Protection**

In the event of a short-circuit or high current at an OUT\_ output, the load current is limited on a per-channel basis to  $I_{LIM}_{HS}$  for the high-side (HS) driver and to  $I_{LIM}_{PP}$ for the low-side (LS) driver. A short-circuit or overcurrent generally creates a temperature rise in the chip; both the HS and LS FETs' temperatures are continuously monitored. When any switch temperature exceeds  $T_{JSHDN}$ , the corresponding OUT\_ output is put in a high-impedance state until the temperature falls by the hysteresis.

If the case temperature is below  $T_{CSHDN}$ , a short circuit on one output will allow the other outputs to operate normally.

The HS current-limit circuit features a controlled dV/dI slope that improves stability with inductive loads. In other words, the current is limited to a nonconstant value that increases with ( $V_{DD}$  -  $V_{OUT}$ ) with a slope of 1A/150V.

Figure 5. Watchdog Timer

### Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Undervoltage Lockout**

When the V<sub>L</sub>, V<sub>DD</sub>, or V<sub>5</sub> supply voltages are under their respective UVLO thresholds, all OUT\_ outputs are turned off (three-stated) and the open-load detect current sources are turned off; they automatically turn back on once the V<sub>DD</sub>/V<sub>5</sub> rises to above the UVLO thresholds.

Undervoltage conditions can be read out through SPI.

The UVLO open-drain output pin indicates whether  $V_{DD}$  is below the  $V_{DD}$   $_{UV}$  threshold.

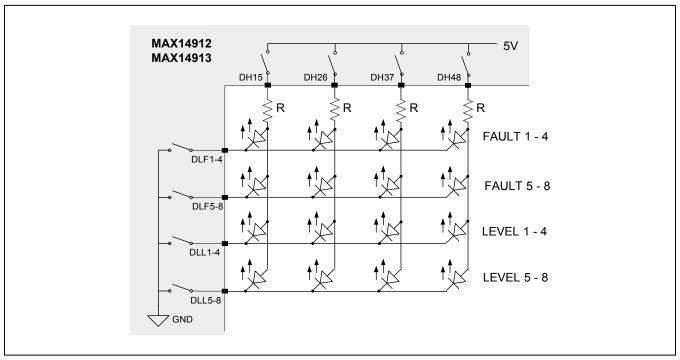

#### **LED Drivers**

The 4 x 4 LED driver crossbar matrix offers a pin-optimized configuration for driving 16 LEDs. Per-channel output status and the fault conditions are indicated by individual LEDs. If a FAULT LED is turned on for an output, the corresponding LEVEL LED is always turned off. This mitigates false information about the status of the affected OUT\_ pin.

For every current-limiting resistor (R), each of the four LEDs in the vertical string are pulsed so that current only flows through one LED at any given time. Therefore, the resistors (R) determine the LED current through one LED

and should be chosen according to the LED's current/lightintensity requirements. Every LED that is on, is pulsed on with a 25% duty cycle.

#### **Configuration and Monitoring**

The MAX14912/MAX14913 can be configured, set, and monitored through either a parallel or serial interface. The serial interface allows greater configuration flexibility and provides more monitoring information. For the MAX14913, in parallel setting mode (SRIAL = low), the SPI cannot be used for configuring the device, SPI is only available for monitoring.

#### **Global Configuration**

Pin-based configuration does not require the use of the SPI interface. It is global and allows for the configuration of all OUT\_ as high-side outputs, push-pull outputs, and enables open-load detection. See Table 1 for details.

In cases where configuration is possible through the parallel and/or serial interface, <u>Table 2</u> documents the priority.

Figure 6. LED Output Status and Fault-Detection Matrix

# Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Table 1. Global Configuration Pins**

| INPUT    | SRIAL | CONFIGURATION                                                                                                                                                                                  |

|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUSHPL   | х     | Configures all OUT_ outputs as push-pull or high-side.<br>0 = All drivers in high-side mode unless configured as push-pull by serial interface.<br>1 = All drivers in push-pull mode.          |

| OL/IN1   | 1     | Enables global open-load detection in serial mode.<br>0 = Open-load detection disabled unless enabled by serial interface.<br>1 = Open-load detection enabled for all high-side mode switches. |

| CRC/IN3  | 1     | Enables CRC generation and error detection on the serial interface.<br>0 = CRC error detection disabled.<br>1 = CRC error detection enabled.                                                   |

| FLTR     | х     | Enables anti-glitch filtering on all logic input pins except SDI and CLK. (Note 1)<br>0 = Glitch filtering disabled.<br>1 = Glitch filtering enabled.                                          |

| WDEN/IN5 | 1     | Enables watchdog on the SPI interface.<br>0 = Watchdog disabled.<br>1 = Watchdog enabled.                                                                                                      |

Note 1: PUSHPL and SRIAL are always filtered, independent of FLTR logic.

#### **Table 2. Configuration Priority**

| CONFIGURATION           | SRIAL | PRIORITY |                                                                                                           |  |  |  |  |

|-------------------------|-------|----------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

|                         | 1     | PUSHPL   | RESULT                                                                                                    |  |  |  |  |

| Push-Pull/<br>High-Side |       | Low      | OUT_ drivers in high-side mode, unless configured individually as push-pull through the serial interface. |  |  |  |  |

| riigii oldo             |       | High     | All OUT_ drivers in push-pull mode, independent of serial configuration.                                  |  |  |  |  |

|                         | 1     | OL/IN1   | RESULT                                                                                                    |  |  |  |  |

| Open-Load Detection     |       | Low      | Open-load detection off, unless configured individually through the serial interface.                     |  |  |  |  |

|                         |       | High     | Open-load detection enabled on all OUT_ outputs that operate in high-side mode.                           |  |  |  |  |

### Octal High-Speed, High-Side Switch/Push-Pull Driver

#### Parallel Interface: Setting the OUT\_ Output Driver

The parallel mode (SRIAL = low) uses one input pin (IN\_) to set each output (OUT\_). Table 3 shows the settings that depend on the configured mode.

In parallel setting mode (SRIAL = low), the MAX14913 can only be configured via the global configuration inputs: PUSHPL and FLTR, not on a per-channel basis through SPI. This means that all high-side drivers are either in high-side or push-pull operation. Open-load detection is enabled and cannot be disabled in parallel setting mode.

The MAX14912 can be configured with full flexibility in parallel setting mode.

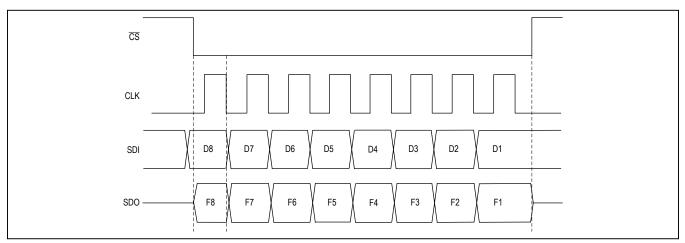

#### Serial Controller Interface

The serial interface can be used in all setting modes. It is based on CPOL = low and CPHA = low, meaning that the SDI data is latched-in on the rising edge of CLK and new SDO data is written on the falling edge of CLK. The default idle CLK state needs to be low. The SDO output is only actively driven when the SPI master drives  $\overline{CS}$  low, it is otherwise weakly pulled down by an internal 200k $\Omega$ resistor when  $\overline{CS}$  is high.

#### Table 3. SRIAL = Low

| DRIVER MODE | IN_ | OUT_ STATE            |

|-------------|-----|-----------------------|

| High-Side   | 0   | High-side off         |

| High-Side   | 1   | High-side on          |

| Push-Pull   | 0   | Push-pull output low  |

| Push-Pull   | 1   | Push-pull output high |

The SPI interface provides per channel and detailed global diagnostics. In serial setting mode (SRIAL = high), the outputs are set on/off/high/low by the serial interface. Serial mode also allows per channel and global configuration. In parallel setting mode (SRIAL = low), the MAX14913 does not allow configuration through SPI, while the MAX1912 can be configured per channel and globally.

The SPI interface can be operated in either command mode or direct mode. Command mode is available in both parallel and serial modes and provides higher information content and supports more configuration options. See <u>Table 4</u> for details. Direct mode SPI is only available in serial setting mode (SRIAL = high). In direct SPI mode, output setting and per channel configuration is written directly (without a command byte) and diagnostics data is provided either in an 8 or 16-bit SPI cycle.

In both command and direct SPI modes, when the highside/push-pull drivers are set on/off/high/low via SPI, the outputs change state at the end of the SPI cycle, on the rising  $\overline{CS}$  edge, with a sub 1µs propagation delay, as defined in the Electrical Properties Table. In direct and command mode SPI, diagnostic and status information is sampled at the beginning of each SPI cycle, initiated by the falling  $\overline{CS}$  edge and is then sequentially written out on SDO on each falling CLK edge. Command SPI mode allows reading back the chip configuration and status and diagnostics, as selected via the command byte. This information is then written out on the following SPI cycle.

#### Table 4. SPI interface Modes Selection and Description

|                       |       | PIN          |              |             | RESULT                                                                                                  |                                                    |                                |                                                                                                          |                           |

|-----------------------|-------|--------------|--------------|-------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------|

| SPI<br>MODE           | SRIAL | CMND<br>/IN2 | CNFG<br>/IN7 | S16<br>/IN8 | BITS                                                                                                    | SDI                                                | SDO                            | NOTES                                                                                                    |                           |

| NC                    |       |              |              | 0           | 8                                                                                                       | Per-channel OUT_<br>setting                        | Per-channel fault              | OUT set by SPI. FAULT is the                                                                             |                           |

| UT SPI<br>OPERATION   | 1     | 0            | 0            | 1           | 16                                                                                                      | Per-channel OUT_<br>setting and HS/PP<br>selection | Per-channel fault<br>and level | real-time status of the fault (driver shutdown or open-load)                                             |                           |

| DIREC<br>8-BIT/16-BIT |       |              |              | 0           | 8                                                                                                       | Per-channel config:<br>HS/PP                       | Per-channel fault              |                                                                                                          |                           |

| 8-BIT/                | 1     | 0            | 1            | 1           | 16     Per-channel config:<br>HS/PP and OL<br>detection on/off     Per-channel fault<br>and level     C |                                                    | 16 HS/PP and OL and level      |                                                                                                          | OUT level does not change |

| AND                   | 1     | 1            | x            | х           | 16                                                                                                      | 8-bit-command +Previous command8-bit dataoutput    |                                | OUT level may or may not change depending on command                                                     |                           |

| COMMAND<br>MODE       | 0     | x            | х            | х           | 16                                                                                                      | 8-bit-command +<br>8-bit data                      | Previous command output        | OUT set by INx pins. MAX14912<br>allows SPI configuration. MAX14913<br>does not allow SPI configuration. |                           |

### Octal High-Speed, High-Side Switch/Push-Pull Driver

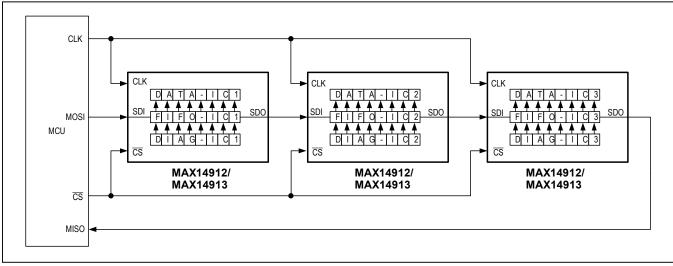

#### **Daisy-Chain SPI Operation**

The device supports daisy-chain operation, allowing control/ monitoring of multiple MAX14912/MAX14913 devices from a single serial interface with one common chip-select signal. The identical data that is clocked into SDI, is clocked out of SDO with a one SPI cycle delay. This is illustrated in Figure 8.

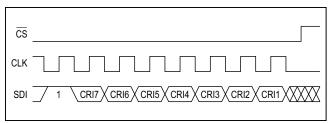

#### Direct SPI Serial Interface: 8-bit Mode

SRIAL = high, CMND = low, S16 = low.

Figure 9 shows an 8-bit cycle that reads the per-channel diagnostic data and sets/configures the outputs in a single 8-bit cycle. Table 5 illustrates the meaning of the SPI bits.

The data returned on SDO is the per-channel fault status.

Pin CNFG is used to select whether the SDI input bits set the output level or the output mode (high-side or pushpull).

Figure 7. Daisy-Chain Connection

Figure 8. SPI Cycle in 8-Bit Direct SPI Mode

# Octal High-Speed, High-Side Switch/Push-Pull Driver

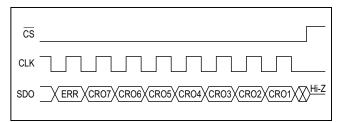

#### Direct SPI Serial Interface: 16-Bit Mode

SRIAL = High, CMND = Low, S16 = High

Figure 9 shows a 16-bit read/write cycle that reads the per-channel diagnostic data and configures/sets the outputs in a single 16-bit cycle.

The data returned on SDO is the per-channel fault status.

The CNFG pin is used to select whether the input bits sent to SDI set the output level or the output mode (high-side or push-pull). Moreover, in 16-bit mode, the open-load detection can be enabled on a per-channel basis.

# Table 5. 8-Bit SPI Direct Mode BitDefinition

| BIT | BIT VALUE | CNFG | DEFINITION                                                                            |

|-----|-----------|------|---------------------------------------------------------------------------------------|

|     | 0         | Low  | In high-side mode: set HS off<br>In push-pull mode: HS off, LS on                     |

| D_  | 1         | Low  | In high-side mode: set HS switch on<br>In push-pull mode: set HS switch<br>on, LS off |

|     | 0         | High | Configure high-side mode                                                              |

|     | 1 Higl    |      | Configure push-pull mode                                                              |

|     | 0         | Х    | No fault                                                                              |

| F_  | 1         | х    | Fault (thermal protection or open load                                                |

# Table 6. 16-Bit SPI Direct Mode BitDefinition

| BIT  | BIT VALUE | CNFG | DEFINITION                                                            |  |  |

|------|-----------|------|-----------------------------------------------------------------------|--|--|

| D_   | 0         | Low  | In high-side mode: HS off, LS off<br>In push-pull mode: HS off, LS on |  |  |

|      | 1         | Low  | HS on, LS off                                                         |  |  |

|      | 0         | Low  | High-side mode                                                        |  |  |

| C_   | 1         | Low  | Push-pull mode                                                        |  |  |

|      | 00 High   |      | High-side mode; open-load detection<br>defined by OL/IN1 pin          |  |  |

| D_C_ | 01        | High | Push-pull mode                                                        |  |  |

|      | 10        | High | High-side mode with open-load detection                               |  |  |

|      | 11        | High | Not used                                                              |  |  |

|      | 0         | Х    | No fault                                                              |  |  |

| F_ 1 |           | х    | Fault status (thermal protection or open-<br>load)                    |  |  |

| L_   | 0         | Х    | Output level < 7V                                                     |  |  |

|      | 1         | Х    | Output level > 7V                                                     |  |  |

Figure 9. SPI Cycle in 16-Bit Direct SPI Mode

### Octal High-Speed, High-Side Switch/Push-Pull Driver

#### **Command Mode SPI**

#### CMND = High

In serial setting mode (SRIAL = high), command SPI mode allows setting, configuration and monitoring. In parallel setting mode (SRIAL = low) command mode allows monitoring. While the MAX14912 supports SPI configuration in parallel mode, configuration is not supported in the MAX14913. In command mode, the input is always a command + data word; pins CNFG, S16, and OL are ignored. The output word returns the information requested during the previous SPI cycle.

Table 7 lists the registers accessible in command mode, while Table 8 lists the commands and their effect.

In command mode, a latched version of all faults is available. In other words, the device keeps any fault in memory until the user decides to clear the fault registers. Each bit of fault registers 4, 5, and 6 is set as soon as its corresponding real-time fault signal goes high. At the end of any SPI cycle during which the SDI MSB (the Z bit) has been set to 1, all fault registers are cleared at once (see Table 8). If [SRIAL = high and CMND = high], the global FAULT signal is latched as well (see Table 9 for more details on the global FAULT signal). Otherwise, it is a real-time global fault status.

In command mode, both the latched and the real-time faults can be read out. All commands except #4 returns the same real-time data as in the 16-bit mode. Command #4 can be used to read any register and, for fault registers 4, 5, and 6, it returns both the latched and real-time value of any fault signal.

| lable | <u>e 7. S</u> | <u>PI REGISTERS (A</u>                                  | ccessib | le Only  | in COM                    | MAND I            | Node)     |         |                         |                         |

|-------|---------------|---------------------------------------------------------|---------|----------|---------------------------|-------------------|-----------|---------|-------------------------|-------------------------|

| REG   | R/W           | PURPOSE                                                 | 7       | 6        | 5                         | 4                 | 3         | 2       | 1                       | 0                       |

| 0     | 0 R/W         | Switch/Driver Settings<br>(Note 2)                      | IN8     | IN7      | IN6                       | IN5               | IN4       | IN3     | IN2                     | IN1                     |

|       |               | Default                                                 | 0       | 0        | 0                         | 0                 | 0         | 0       | 0                       | 0                       |

| 1     | R/W           | Push-Pull/High-Side<br>Configuration (Note 3)           | PP8     | PP7      | PP6                       | PP5               | PP4       | PP3     | PP2                     | PP1                     |

|       |               | Default                                                 | 0       | 0        | 0                         | 0                 | 0         | 0       | 0                       | 0                       |

| 2     | R/W           | Open Load Detect<br>Enable (Note 3)                     | OL_EN8  | OL_EN7   | OL_EN6                    | OL_EN5            | OL_EN4    | OL_EN3  | OL_EN2                  | OL_EN1                  |

|       |               | Default                                                 | 0       | 0        | 0                         | 0                 | 0         | 0       | 0                       | 0                       |

| 3     | R/W           | Watchdog Config. And<br>Channel Paralleling<br>(Note 3) | _       | _        | _                         | _                 | joinUP    | joinDW  | WD1                     | WD0                     |

|       |               | Default                                                 | 0       | 0        | 0                         | 0                 | 0         | 0       | 0                       | 0                       |

| 4     | R             | Per-Channel Open-Load<br>Condition                      | OL8*    | OL7*     | OL6*                      | OL5*              | OL4*      | OL3*    | OL2*                    | OL1*                    |

| 5     | R             | Per-Channel Thermal<br>Shutdown                         | THSD8*  | THSD7*   | THSD6*                    | THSD5*            | THSD4*    | THSD3*  | THSD2*                  | THSD1*                  |

| 6     | R             | Global Faults                                           | WDfault | CRCfault | DCDC<br>Current-<br>Limit | 8CKmult<br>Error* | THSDglob* | 5V UVLO | V <sub>DD</sub><br>UVLO | V <sub>DD</sub><br>WARN |