# CMOS Static RAM 1 Meg (128K x 8-Bit)

#### IDT71024S

#### Features

- 128K x 8 advanced high-speed CMOS static RAM

- ◆ Commercial (0°C to +70°C), Industrial (-40°C to +85°C)

- Equal access and cycle times

Commercial and Industrial: 12/15/20ns

- Two Chip Selects plus one Output Enable pin

- Bidirectional inputs and outputs directly TTL-compatible

- Low power consumption via chip deselect

- Available in 300 and 400 mil Plastic SOJ.

## Description

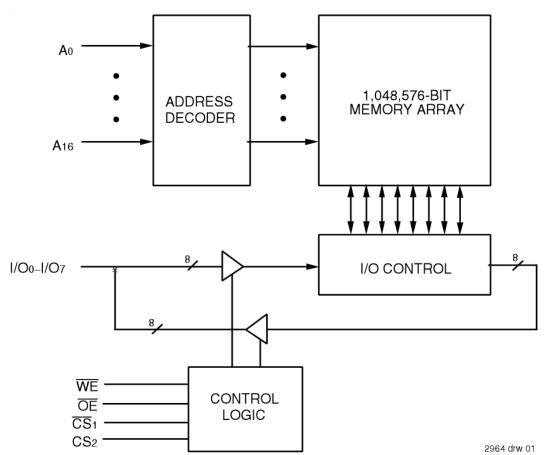

The IDT71024 is a 1,048,576-bit high-speed static RAM organized as  $128 \, \text{K} \, \text{x} \, 8$ . It is fabricated using high-performance, high-reliability CMOS technology. This state-of-the-art technology, combined with innovative circuit design techniques, provides a cost-effective solution for high-speed memory needs.

The IDT71024 has an output enable pin which operates as fast as 6ns, with address access times as fast as 12ns available. All bidirectional inputs and outputs of the IDT71024 are TTL-compatible, and operation is from a single 5V supply. Fully static asynchronous circuitry is used; no clocks or refreshes are required for operation.

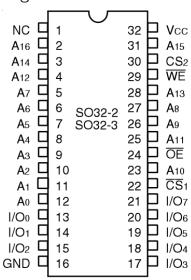

The IDT71024 is packaged in 32-pin 300 mil Plastic SOJ and 32-pin 400 mil Plastic SOJ.

## Functional Block Diagram

FEBRUARY 2013

## Pin Configuration

SOJ Top View

2964 drw 02

## Truth Table<sup>(1,3)</sup>

| Inputs |                    |                    |    |         |                             |

|--------|--------------------|--------------------|----|---------|-----------------------------|

| WE     | <del>CS</del> ₁    | CS <sub>2</sub>    | ŌĒ | I/O     | Function                    |

| Х      | Н                  | Χ                  | Χ  | High-Z  | Deselected – Standby (ISB)  |

| Х      | VHC <sup>(2)</sup> | Х                  | Χ  | High-Z  | Deselected – Standby (ISB1) |

| Х      | Χ                  | L                  | Χ  | High-Z  | Deselected – Standby (ISB)  |

| Χ      | Χ                  | VLC <sup>(2)</sup> | Χ  | High-Z  | Deselected – Standby (ISB1) |

| Н      | L                  | Н                  | Н  | High-Z  | Outputs Disabled            |

| Н      | L                  | Н                  | L  | DATAout | Read Data                   |

| L      | L                  | Н                  | Χ  | DATAIN  | Write Data                  |

#### NOTES:

- 1.  $H = V_{IH}, L = V_{IL}, X = Don't care.$

- 2. VLC = 0.2V, VHC = VCC 0.2V.

- 3. Other inputs  $\geq$ VHC or  $\leq$ VLC.

## Recommended Operating Temperature and Supply Voltage

| Grade      | Temperature    | GND | <b>V</b> cc |

|------------|----------------|-----|-------------|

| Commercial | 0°C to +70°C   | 0V  | 5.0V ± 0.5V |

| Industrial | –40°C to +85°C | 0V  | 5.0V ± 0.5V |

2964 tbl 05

2964 tbl 01

# Absolute Maximum Ratings(1)

| Symbol               | Rating                               | Value        | Unit |

|----------------------|--------------------------------------|--------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage with Respect to GND | -0.5 to +7.0 | ٧    |

| TBIAS                | Temperature Under Bias               | -55 to +125  | ٥C   |

| Тѕтс                 | Storage Temperature                  | -55 to +125  | ٥C   |

| Рт                   | Power Dissipation                    | 1.25         | W    |

| Іоит                 | DC Output Current                    | 50           | mA   |

NOTES:

2964 tbl 02

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

- 2. VTERM must not exceed Vcc + 0.5V.

## Capacitance

(TA = +25°C, f = 1.0MHz, SOJ package)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| Cin    | Input Capacitance        | VIN = 3dV  | 7    | pF   |

| Cı/o   | I/O Capacitance          | Vout = 3dV | 8    | pF   |

2964 tbl 03

2964 tbl 04

NOTE:

1. This parameter is guaranteed by device characterization, but is not production tested.

# Recommended DC Operating Conditions

| Symbol | Parameter          | Min.                | Тур. | Max.    | Unit |

|--------|--------------------|---------------------|------|---------|------|

| Vcc    | Supply Voltage     | 4.5                 | 5.0  | 5.5     | V    |

| GND    | Ground             | 0                   | 0    | 0       | V    |

| VIH    | Input High Voltage | 2.2                 | _    | Vcc+0.5 | V    |

| VIL    | Input Low Voltage  | -0.5 <sup>(1)</sup> | _    | 0.8     | V    |

NOTE:

1. VIL (min.) = -1.5V for pulse width less than 10ns, once per cycle.

### DC Electrical Characteristics

(Vcc = 5.0V ± 10%, Commercial and Industrial Temperature Ranges)

|        |                        |                                                                            | IDT7 |      |      |

|--------|------------------------|----------------------------------------------------------------------------|------|------|------|

| Symbol | Parameter              | Test Condition                                                             | Min. | Max. | Unit |

| lu     | Input Leakage Current  | Vcc = Max., Vin = GND to Vcc                                               | -    | 5    | μΑ   |

| lLO    | Output Leakage Current | Vcc = Max., $\overline{\text{CS}}_1$ = V <sub>IH</sub> , Vout = GND to Vcc | _    | 5    | μΑ   |

| Vol    | Output Low Voltage     | IoL = 8mA, Vcc = Min.                                                      | _    | 0.4  | ٧    |

| Vон    | Output High Voltage    | IOH = -4mA, Vcc = Min.                                                     | 2.4  | _    | V    |

2964 tbl 06

## DC Electrical Characteristics<sup>(1)</sup>

$(VCC = 5.0V \pm 10\%, VLC = 0.2V, VHC = VCC - 0.2V)$

|        |                                                                                                                                                                                    | 7102   | 4S12 | 7102   | 4S15 | 7102   | 4S20 |      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--------|------|--------|------|------|

| Symbol | Parameters                                                                                                                                                                         | Com'l. | Ind. | Com'l. | Ind. | Com'l. | Ind. | Unit |

| lcc    | Dynamic Operating Current, $CS_2 \ge VIH$ and $\overline{CS}_1 \le VIL$ , Outputs Open, $VCC = Max.$ , $f = f_{MAX}^{(2)}$                                                         | 160    | 160  | 155    | 155  | 140    | 140  | mA   |

| ISB    | Standby Power Supply Current (TTL Level) $\overline{CS}_1 \ge V_{IH}$ or $CS_2 \le V_{IL}$ , Outputs Open, $Vcc = Max.$ , $f=f_{Max}(^2)$                                          | 40     | 40   | 40     | 40   | 40     | 40   | mA   |

| ISB1   | Full Standby Power Supply Current (CMOS Level), $\overline{CS}_1 \ge V$ HC or $CS_2 \le V$ LC, Outputs Open, $V$ CC = Max., $f = 0^{(2)}$ , $V$ IN $\le V$ LC or $V$ IN $\ge V$ HC | 10     | 10   | 10     | 10   | 10     | 10   | mA   |

#### NOTES:

- 1. All values are maximum guaranteed values.

- 2.  $f_{MAX} = 1/t_{RC}$  (all address inputs are cycling at  $f_{MAX}$ ); f = 0 means no address input lines are changing.

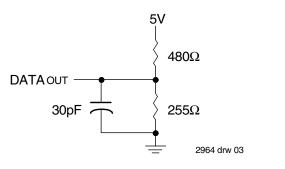

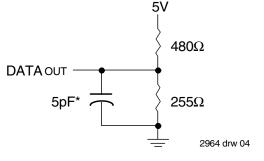

### AC Test Conditions

| Input Pulse Levels            | GND to 3.0V         |

|-------------------------------|---------------------|

| Input Rise/Fall Times         | 3ns                 |

| Input Timing Reference Levels | 1.5V                |

| Output Reference Levels       | 1.5V                |

| AC Test Load                  | See Figures 1 and 2 |

2964 tbl 08

Figure 1. AC Test Load

2964 tbl 07

\*Including jig and scope capacitance.

Figure 2. AC Test Load (for tclz, tolz, tchz, tohz, tow, and twhz)

# AC Electrical Characteristics

(Vcc = 5.0V ± 10%, Commercial and Industrial Temperature Ranges)

|                     |                                    | 7102 | 24S12 | 7102 | 24S15 | 71024S20 |      |      |

|---------------------|------------------------------------|------|-------|------|-------|----------|------|------|

| Symbol              | Parameter                          | Min. | Max.  | Min. | Max.  | Min.     | Max. | Unit |

| Read Cycle          |                                    | •    |       |      |       |          |      |      |

| trc                 | Read Cycle Time                    | 12   | _     | 15   | _     | 20       | _    | ns   |

| taa                 | Address Access Time                | _    | 12    | _    | 15    | _        | 20   | ns   |

| tacs                | Chip Select Access Time            | _    | 12    | _    | 15    | _        | 20   | ns   |

| tcLz <sup>(1)</sup> | Chip Select to Output in Low-Z     | 3    | _     | 3    | _     | 3        | _    | ns   |

| tcHz <sup>(1)</sup> | Chip Deselect to Output in High-Z  | 0    | 6     | 0    | 7     | 0        | 8    | ns   |

| toe                 | Output Enable to Output Valid      | _    | 6     | _    | 7     | _        | 8    | ns   |

| tolz <sup>(1)</sup> | Output Enable to Output in Low-Z   | 0    | _     | 0    | _     | 0        | _    | ns   |

| toнz <sup>(1)</sup> | Output Disable to Output in High-Z | 0    | 5     | 0    | 5     | 0        | 7    | ns   |

| tон                 | Output Hold from Address Change    | 4    | _     | 4    | _     | 4        | -    | ns   |

| tpu <sup>(1)</sup>  | Chip Select to Power-Up Time       | 0    | _     | 0    | _     | 0        | _    | ns   |

| tpD <sup>(1)</sup>  | Chip Deselect to Power-Down Time   | _    | 12    | _    | 15    | _        | 20   | ns   |

| Write Cycle         |                                    |      |       |      |       |          |      |      |

| twc                 | Write Cycle Time                   | 12   | _     | 15   | _     | 20       | -    | ns   |

| taw                 | Address Valid to End-of-Write      | 10   | _     | 12   | _     | 15       | 1    | ns   |

| tcw                 | Chip Select to End-of-Write        | 10   | _     | 12   | _     | 15       |      | ns   |

| tas                 | Address Set-Up Time                | 0    | _     | 0    | _     | 0        | _    | ns   |

| twp                 | Write Pulse Width                  | 8    | _     | 12   | _     | 15       | -    | ns   |

| twr                 | Write Recovery Time                | 0    | _     | 0    | _     | 0        | _    | ns   |

| tow                 | Data Valid to End-of-Write         | 7    | _     | 8    | _     | 9        | _    | ns   |

| tон                 | Data Hold Time                     | 0    | _     | 0    | _     | 0        | _    | ns   |

| tow <sup>(1)</sup>  | Output Active from End-of-Write    | 3    |       | 3    | _     | 4        |      | ns   |

| twHz <sup>(1)</sup> | Write Enable to Output in High-Z   | 0    | 5     | 0    | 5     | 0        | 8    | ns   |

NOTE: 2964 tbl 09

$<sup>1. \</sup>quad \text{This parameter guaranteed with the AC load (Figure 2) by device characterization, but is not production tested.} \\$

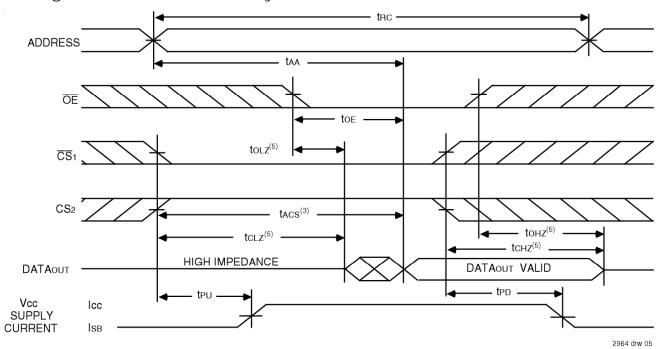

# Timing Waveform of Read Cycle No. 1(1)

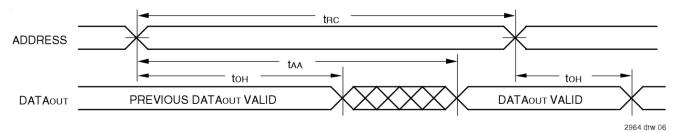

## Timing Waveform of Read Cycle No. 2(1,2,4)

#### NOTES:

- 1. WE is HIGH for Read Cycle.

- 2. Device is continuously selected,  $\overline{\text{CS}}_1$  is LOW, CS2 is HIGH.

- 3. Address must be valid prior to or coincident with the later of  $\overline{CS}_1$  transition LOW and CS2 transition HIGH; otherwise tAA is the limiting parameter.

- 4.  $\overline{\mathsf{OE}}\mathsf{isLOW}.$

- 5. Transition is measured ±200mV from steady state.

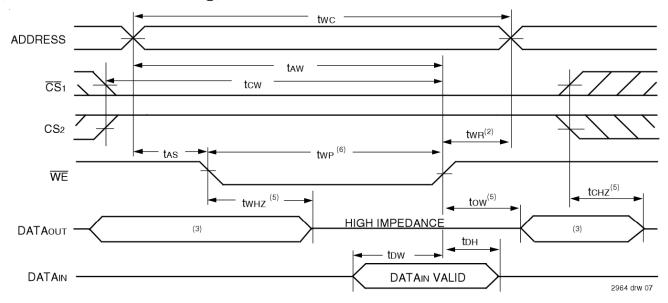

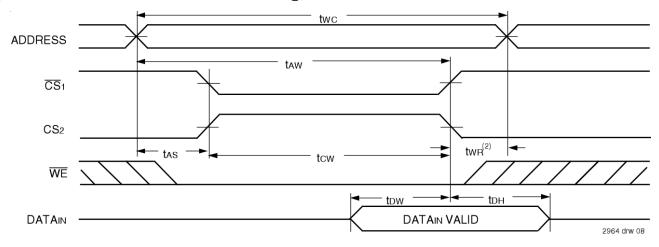

# Timing Waveform of Write Cycle No. 1 (**WE** Controlled Timing)<sup>(1,4,6)</sup>

# Timing Waveform of Write Cycle No. 2 (**CS**<sub>1</sub> AND CS<sub>2</sub> Controlled Timing)<sup>(1,4)</sup>

#### NOTES:

- 1. A write occurs during the overlap of a LOW  $\overline{CS}_1$ , HIGH CS<sub>2</sub>, and a LOW  $\overline{WE}$ .

- 2. twn is measured from the earlier of either  $\overline{\text{CS}}_1$  or  $\overline{\text{WE}}$  going HIGH or CS2 going LOW to the end of the write cycle.

- 3. During this period, I/O pins are in the output state, and input signals must not be applied.

- 4. If the CS1 LOW transition or the CS2 HIGH transition occurs simultaneously with or after the WE LOW transition, the outputs remain in a high impedance state. CS1 and CS2 must both be active during the tcw write period.

- 5.  $\underline{\text{Transition is measured } \pm 200 \text{mV from steady state}}$

- 6.  $\overline{OE}$  is continuously HIGH. During a  $\overline{WE}$  controlled write cycle with  $\overline{OE}$  LOW, twp must be greater than or equal to twHz + tbw to allow the I/O drivers to turn off and data to be placed on the bus for the required tbw. If  $\overline{OE}$  is HIGH during a  $\overline{WE}$  controlled write cycle, this requirement does not apply and the minimum write pulse is the specified twp.

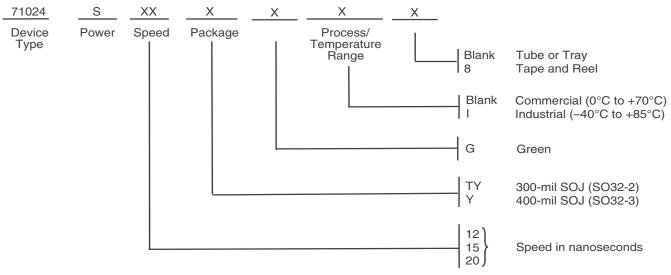

# Ordering Information

2964 drw 09

# Datasheet Document History

| 9/30/99  |                | Updated to newformat                                                                         |

|----------|----------------|----------------------------------------------------------------------------------------------|

|          | Pg. 1, 3, 4, 7 | Added 12ns industrial speed grade offering                                                   |

|          | Pg. 1–4, 7     | Removed military temperature offerings                                                       |

|          | · ·            | Removed 17ns and 25ns speed grades                                                           |

|          | Pg. 3          | Revised Icc and Isb1 for 15ns and 20ns industrial speed grades                               |

|          | Pg. 6          | Removed Note 1, reordered notes and footnotes                                                |

|          | Pg. 8          | Added Datasheet Document History                                                             |

| 1/6/2000 | Pg. 4          | Changed twp(min) for 12ns speed grade from 10ns to 8ns.                                      |

| 2/18/00  | Pg. 3          | Revised Icc and IsB for Industrial Temperature offerings to meet commercial specifications   |

| 3/14/00  | Pg. 3          | Revised IsB to accommodate speed functionality                                               |

| 08/09/00 |                | Not recommended for new designs                                                              |

| 02/01/01 |                | Removed "Not recommended for new designs"                                                    |

| 01/30/04 | Pg. 7          | Added "Restricted hazardous substance device" to the ordering information.                   |

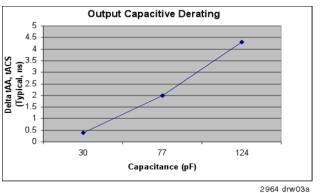

| 05/22/06 | Pg.3           | Added drawing Output Capacitive Derating drawing.                                            |

| 02/13/07 | Pg.7           | Added M generation die step to data sheet ordering information.                              |

| 08/13/09 | Pg.2           | Corrected note reference.                                                                    |

| 02/05/13 | Pg.1           | Removed /MS from datasheet header. Removed IDT's reference to fabrication.                   |

|          | Pg.7           | Updated ordering information by adding Tape and Reel, updated Restricted Hazardous Substance |

|          |                | Device wording to Green and removed the Die Stepping Revision, the "M" designator.           |

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

## Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/